Architecture

(1) DEPC (Debug Exception Program Counter) register (register no.17)

The DEPC register holds the address where processing is to resume after the debug exception has been taken care of.

(Note : DEPC is a read/write register.)

The address that goes in the DEPC register is the virtual address of the instruction that caused the debug exception. If that instruction is in the branch delay slot, the virtual address of the immediately preceding branch or jump instruction goes in this register and Debug register DBD bit is set to 1.

Execution of the DERET instruction causes a jump to the DEPC address.

31 | 0 | |

|

|

|

DEPC

32

Figure 8-2 DEPC register

(Note) When a debug exception occurs, EPC retains its value.

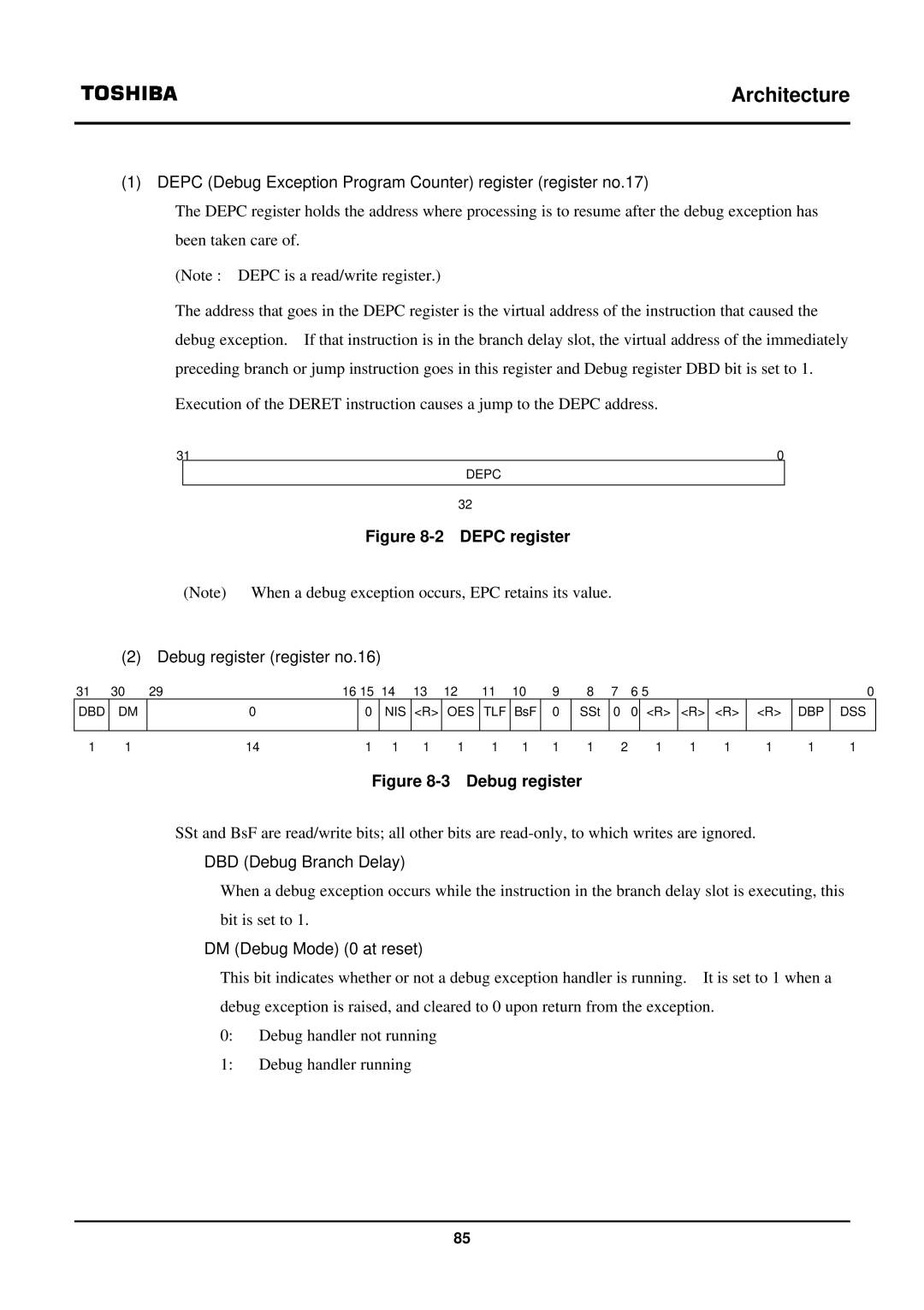

(2) Debug register (register no.16)

31 | 30 | 29 |

| 16 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 5 |

|

|

|

| 0 | ||

DBD | DM |

| 0 |

| 0 | NIS | <R> | OES | TLF | BsF | 0 | SSt | 0 | 0 | <R> | <R> | <R> | <R> | DBP | DSS |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 | 1 |

| 14 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 2 | 1 | 1 | 1 | 1 | 1 | 1 | ||

Figure 8-3 Debug register

SSt and BsF are read/write bits; all other bits are

nDBD (Debug Branch Delay)

When a debug exception occurs while the instruction in the branch delay slot is executing, this bit is set to 1.

nDM (Debug Mode) (0 at reset)

This bit indicates whether or not a debug exception handler is running. It is set to 1 when a debug exception is raised, and cleared to 0 upon return from the exception.

0:Debug handler not running

1:Debug handler running

85