TMPR3901F

4.4 Interrupts

The TMPR3901F supports six hardware interrupts and two software interrupts. It also supports a non- maskable interrupt. The INT[5:0]* signals can be used to raise interrupt exceptions. The NMI* signal is used to raise a non-maskable interrupt exception. All of the interrupt signals are low-active and should be synchronous with SYSCLK rising edge.

4.4.1NMI*

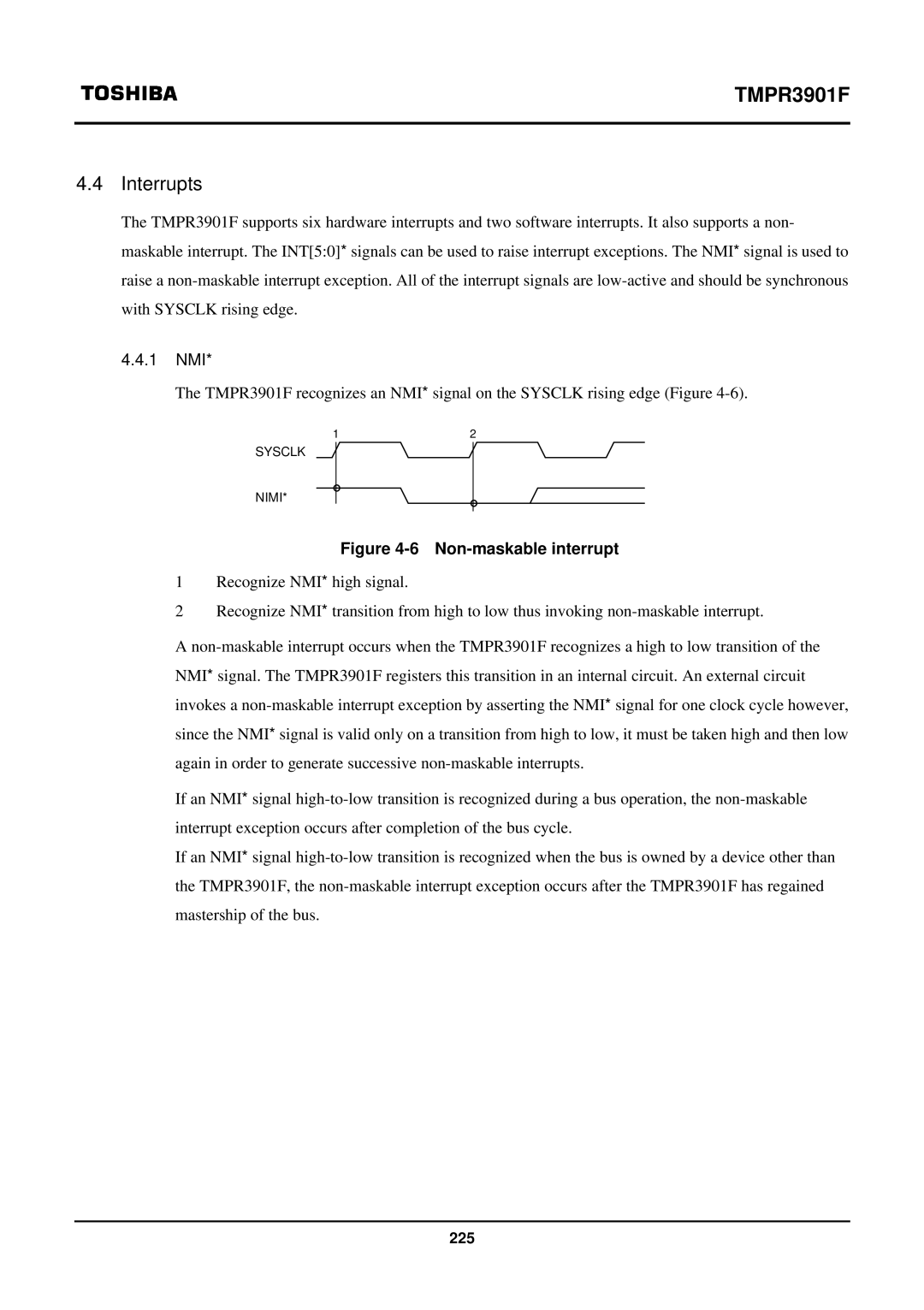

The TMPR3901F recognizes an NMI* signal on the SYSCLK rising edge (Figure 4-6).

SYSCLK

NIMI*

Figure 4-6 Non-maskable interrupt

1Recognize NMI* high signal.

2Recognize NMI* transition from high to low thus invoking non-maskable interrupt.

A non-maskable interrupt occurs when the TMPR3901F recognizes a high to low transition of the NMI* signal. The TMPR3901F registers this transition in an internal circuit. An external circuit invokes a non-maskable interrupt exception by asserting the NMI* signal for one clock cycle however, since the NMI* signal is valid only on a transition from high to low, it must be taken high and then low again in order to generate successive non-maskable interrupts.

If an NMI* signal high-to-low transition is recognized during a bus operation, the non-maskable interrupt exception occurs after completion of the bus cycle.

If an NMI* signal high-to-low transition is recognized when the bus is owned by a device other than the TMPR3901F, the non-maskable interrupt exception occurs after the TMPR3901F has regained mastership of the bus.

225