Architecture

Chapter 7 Caches

The R3900 Processor Core is equipped with separate

Note : Currently only the cache configuration described below is supported. It consists of a 4 Kbyte instruction cache and 1 Kbyte data cache.

7.1 Instruction Cache

The instruction cache has the following specifications.

− Cache size | : 4 Kbytes (Config register ICS bits = 010) |

−Direct mapping

− Block (line) size : 4 words (16 bytes)

−Physical cache

− Burst refill size : Choice of 4/8/16/32 words (set in Config register)

−All valid bits are cleared (made invalid) by a Reset exception

Note : The lock function is not currently supported for the instruction cache. Cache register bits IALc, IALp and IALo do not affect the instruction cache.

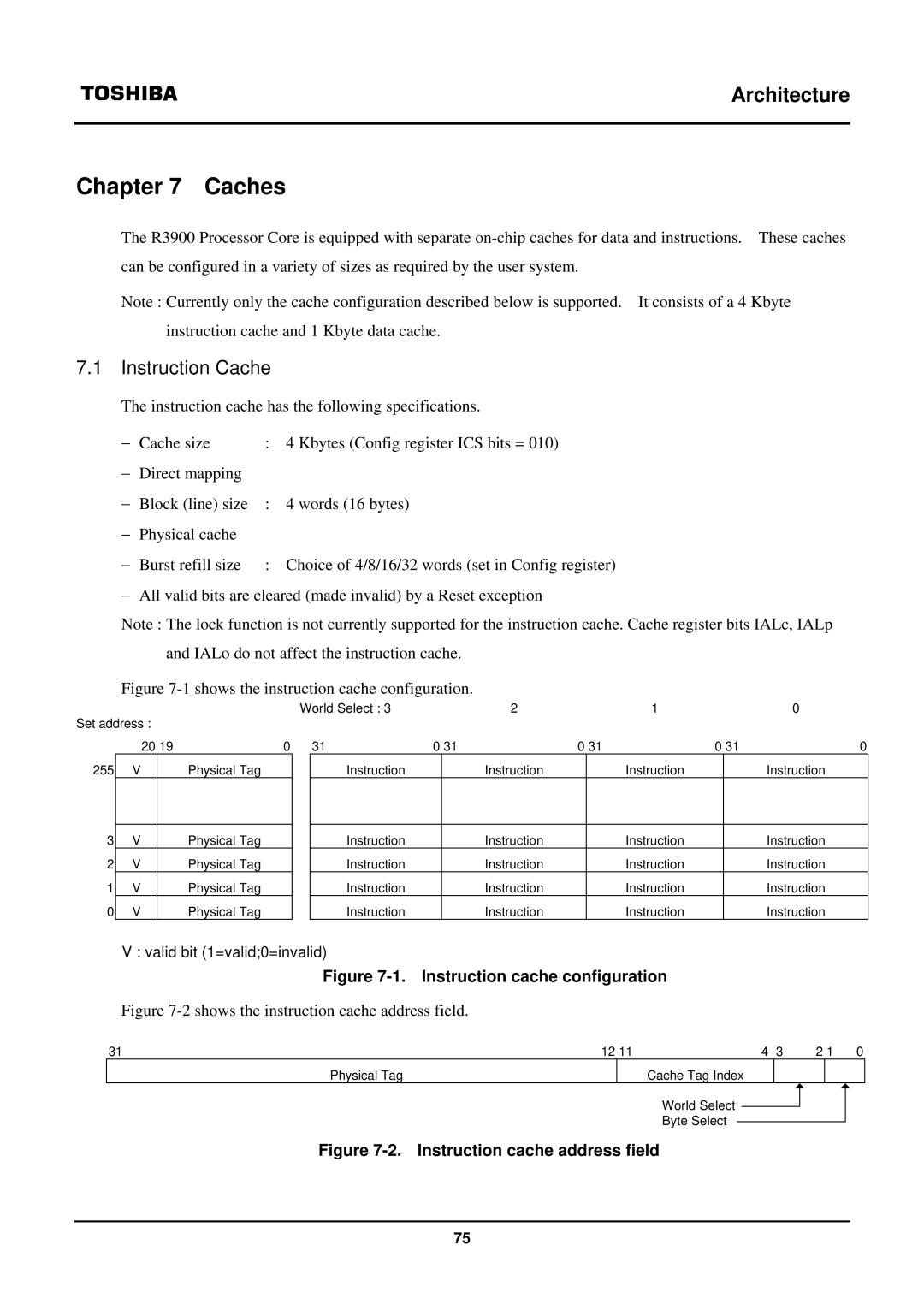

Figure 7-1 shows the instruction cache configuration.

|

|

|

|

| World Select : 3 | 2 |

|

| 1 |

| 0 | ||

Set address : |

|

|

|

|

|

|

|

|

|

|

| ||

| 20 19 |

| 0 | 31 | 0 31 | 0 31 | 0 31 | 0 | |||||

255 | V |

| Physical Tag |

|

| Instruction |

| Instruction |

|

| Instruction |

| Instruction |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

3 | V |

| Physical Tag |

|

| Instruction |

| Instruction |

|

| Instruction |

| Instruction |

2 | V |

| Physical Tag |

|

| Instruction |

| Instruction |

|

| Instruction |

| Instruction |

1 | V |

| Physical Tag |

|

| Instruction |

| Instruction |

|

| Instruction |

| Instruction |

0 | V |

| Physical Tag |

|

| Instruction |

| Instruction |

|

| Instruction |

| Instruction |

V : valid bit (1=valid;0=invalid)

Figure 7-1. Instruction cache configuration

Figure 7-2 shows the instruction cache address field.

31 | 12 11 | 4 | 3 | 2 1 | 0 | ||

Physical Tag |

|

| Cache Tag Index |

|

|

|

|

World Select

Byte Select

Figure 7-2. Instruction cache address field

75