Appendix

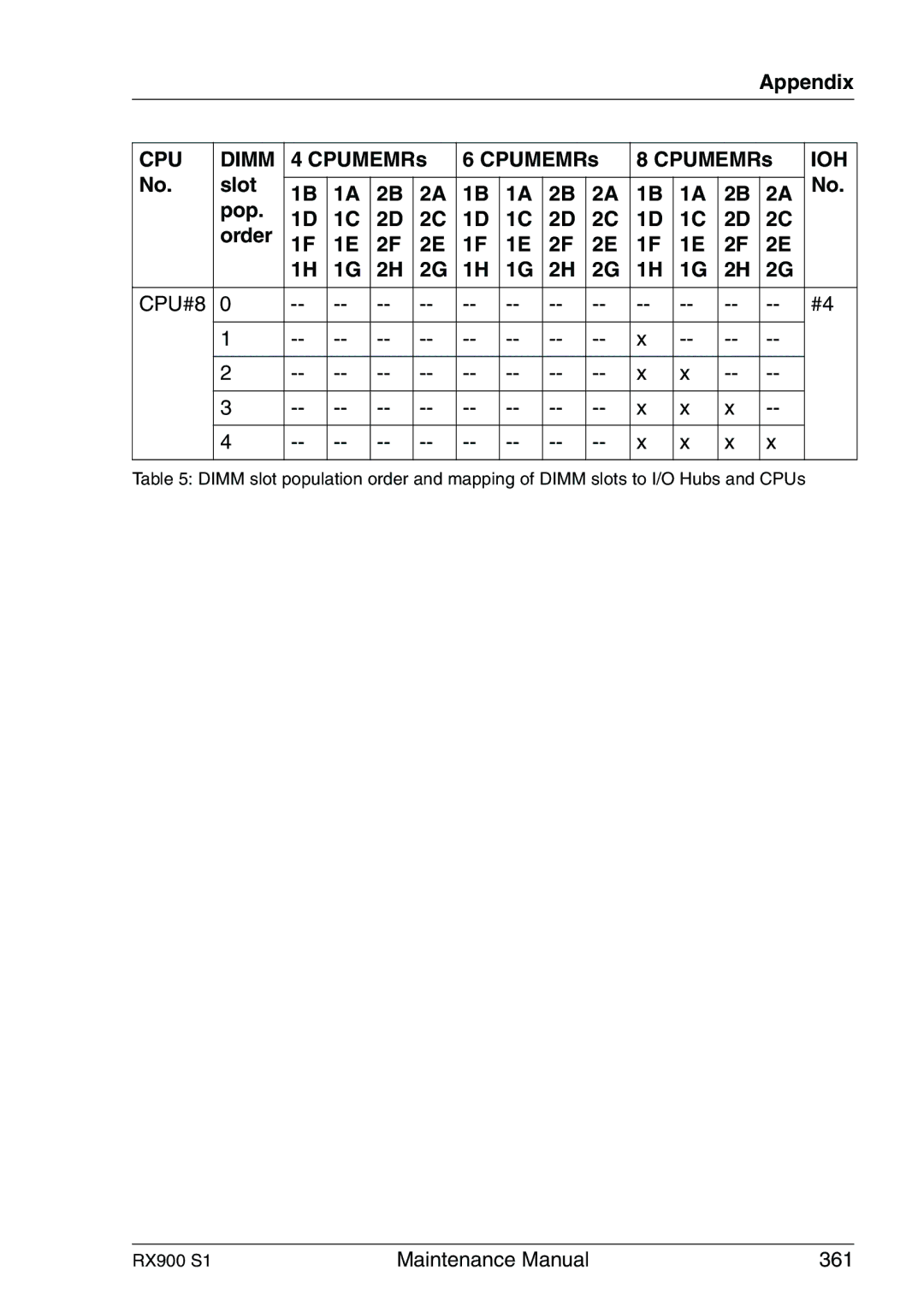

CPU | DIMM | 4 CPUMEMRs | 6 CPUMEMRs | 8 CPUMEMRs | IOH | |||||||||||

No. | slot |

|

|

|

|

|

|

|

|

|

|

|

|

| No. | |

| 1B | 1A | 2B | 2A | 1B | 1A | 2B | 2A | 1B | 1A | 2B | 2A | ||||

|

| pop. | 1D | 1C | 2D | 2C | 1D | 1C | 2D | 2C | 1D | 1C | 2D | 2C |

| |

|

| order |

| |||||||||||||

|

| 1F | 1E | 2F | 2E | 1F | 1E | 2F | 2E | 1F | 1E | 2F | 2E |

| ||

|

|

|

| 1H | 1G | 2H | 2G | 1H | 1G | 2H | 2G | 1H | 1G | 2H | 2G |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CPU#8 | 0 |

| #4 | |||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 1 |

| x |

| |||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 2 |

| x | x |

| ||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 3 |

| x | x | x |

| |||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 4 |

| x | x | x | x |

| ||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Table 5: DIMM slot population order and mapping of DIMM slots to I/O Hubs and CPUs

RX900 S1 | Maintenance Manual | 361 |