AMD | P R E L I M I N A R Y |

|

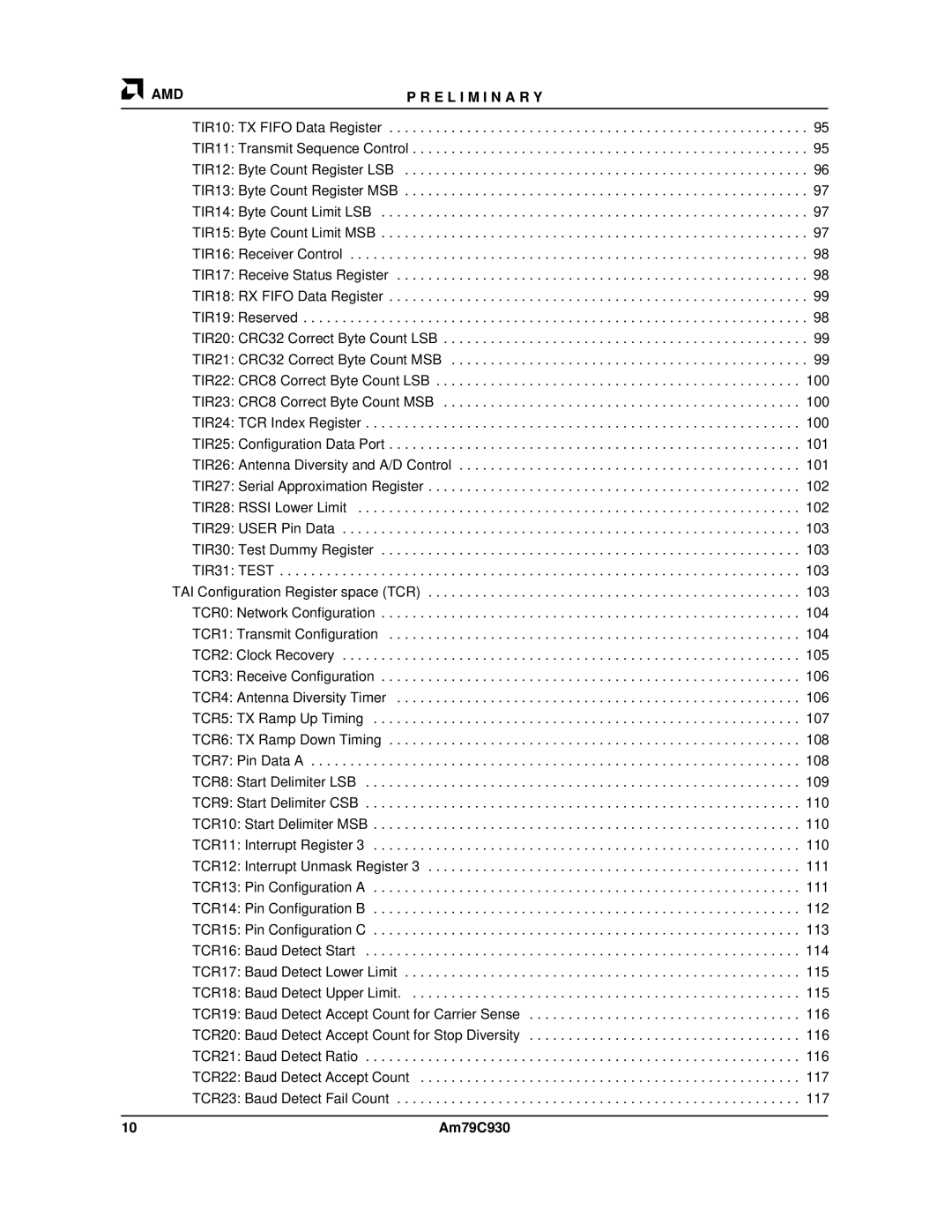

| TIR10: TX FIFO Data Register | . 95 |

| TIR11: Transmit Sequence Control | . 95 |

| TIR12: Byte Count Register LSB | . 96 |

| TIR13: Byte Count Register MSB | . 97 |

| TIR14: Byte Count Limit LSB | . 97 |

| TIR15: Byte Count Limit MSB | . 97 |

| TIR16: Receiver Control | . 98 |

| TIR17: Receive Status Register | . 98 |

| TIR18: RX FIFO Data Register | . 99 |

| TIR19: Reserved | . 98 |

| TIR20: CRC32 Correct Byte Count LSB | . 99 |

| TIR21: CRC32 Correct Byte Count MSB | . 99 |

| TIR22: CRC8 Correct Byte Count LSB | 100 |

| TIR23: CRC8 Correct Byte Count MSB | 100 |

| TIR24: TCR Index Register | 100 |

| TIR25: Configuration Data Port | 101 |

| TIR26: Antenna Diversity and A/D Control | 101 |

| TIR27: Serial Approximation Register | 102 |

| TIR28: RSSI Lower Limit | 102 |

| TIR29: USER Pin Data | 103 |

| TIR30: Test Dummy Register | 103 |

| TIR31: TEST | 103 |

TAI Configuration Register space (TCR) | 103 | |

| TCR0: Network Configuration | 104 |

| TCR1: Transmit Configuration | 104 |

| TCR2: Clock Recovery | 105 |

| TCR3: Receive Configuration | 106 |

| TCR4: Antenna Diversity Timer | 106 |

| TCR5: TX Ramp Up Timing | 107 |

| TCR6: TX Ramp Down Timing | 108 |

| TCR7: Pin Data A | 108 |

| TCR8: Start Delimiter LSB | 109 |

| TCR9: Start Delimiter CSB | 110 |

| TCR10: Start Delimiter MSB | 110 |

| TCR11: Interrupt Register 3 | 110 |

| TCR12: Interrupt Unmask Register 3 | 111 |

| TCR13: Pin Configuration A | 111 |

| TCR14: Pin Configuration B | 112 |

| TCR15: Pin Configuration C | 113 |

| TCR16: Baud Detect Start | 114 |

| TCR17: Baud Detect Lower Limit | 115 |

| TCR18: Baud Detect Upper Limit | 115 |

| TCR19: Baud Detect Accept Count for Carrier Sense | 116 |

| TCR20: Baud Detect Accept Count for Stop Diversity | 116 |

| TCR21: Baud Detect Ratio | 116 |

| TCR22: Baud Detect Accept Count | 117 |

| TCR23: Baud Detect Fail Count | 117 |

10 | Am79C930 |

|