|

|

| P R E L I M I N A R Y | AMD | |

|

|

|

|

| |

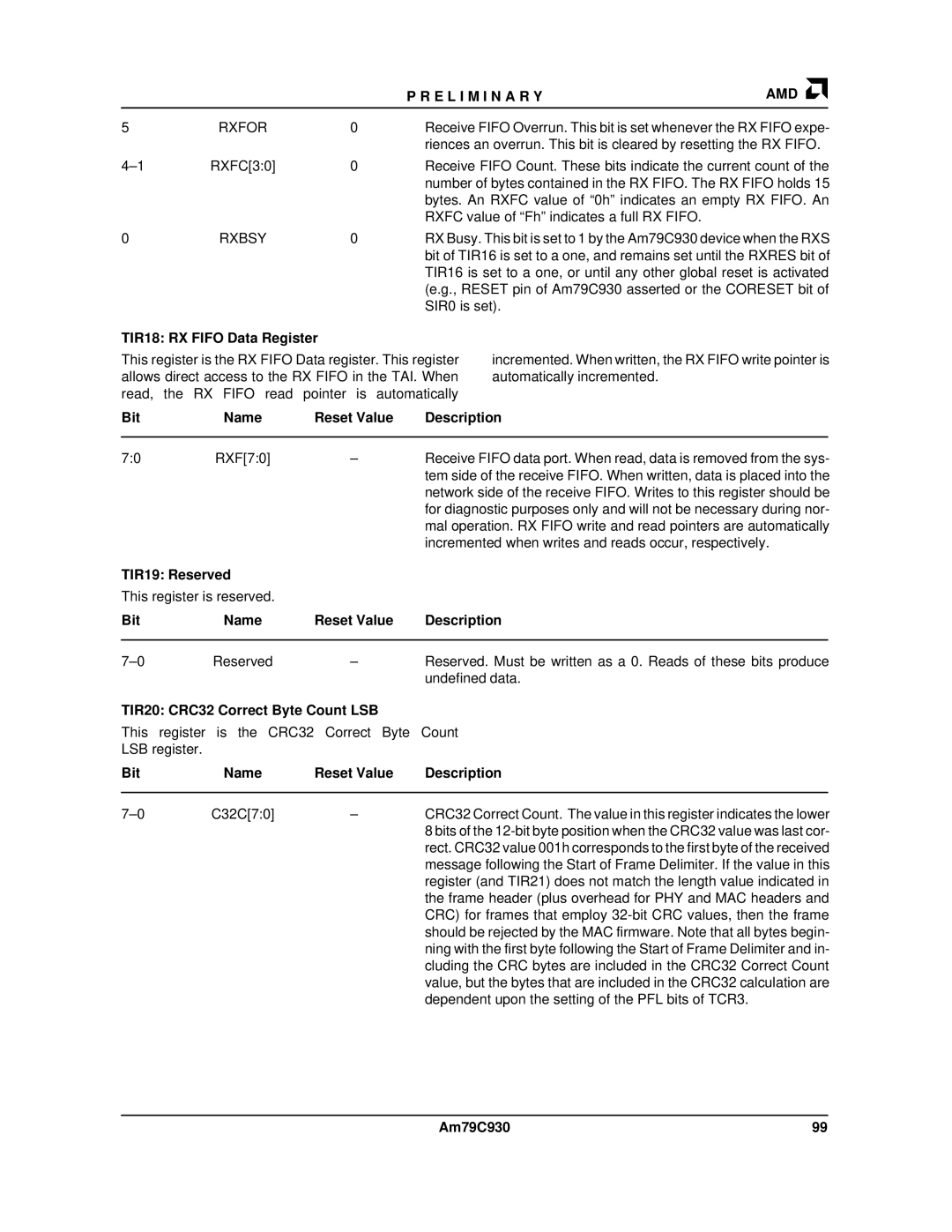

5 | RXFOR | 0 | Receive FIFO Overrun. This bit is set whenever the RX FIFO expe- | ||

|

|

| riences an overrun. This bit is cleared by resetting the RX FIFO. | ||

RXFC[3:0] | 0 | Receive FIFO Count. These bits indicate the current count of the | |||

|

|

| number of bytes contained in the RX FIFO. The RX FIFO holds 15 | ||

|

|

| bytes. An RXFC value of “0h” indicates an empty RX FIFO. An | ||

|

|

| RXFC value of “Fh” indicates a full RX FIFO. |

|

|

0 | RXBSY | 0 | RX Busy. This bit is set to 1 by the Am79C930 device when the RXS | ||

|

|

| bit of TIR16 is set to a one, and remains set until the RXRES bit of | ||

|

|

| TIR16 is set to a one, or until any other global reset is activated | ||

|

|

| (e.g., RESET pin of Am79C930 asserted or the CORESET bit of | ||

|

|

| SIR0 is set). |

|

|

TIR18: RX FIFO Data Register

This register is the RX FIFO Data register. This register allows direct access to the RX FIFO in the TAI. When read, the RX FIFO read pointer is automatically

incremented. When written, the RX FIFO write pointer is automatically incremented.

Bit | Name | Reset Value | Description | |

|

|

|

|

|

7:0 | RXF[7:0] | – | Receive FIFO data port. When read, data is removed from the sys- | |

|

|

| tem side of the receive FIFO. When written, data is placed into the | |

|

|

| network side of the receive FIFO. Writes to this register should be | |

|

|

| for diagnostic purposes only and will not be necessary during nor- | |

|

|

| mal operation. RX FIFO write and read pointers are automatically | |

|

|

| incremented when writes and reads occur, respectively. | |

TIR19: Reserved |

|

|

| |

This register is reserved. |

|

|

| |

Bit | Name | Reset Value | Description | |

|

|

|

|

|

Reserved | – | Reserved. Must be written as a 0. Reads of these bits produce | ||

|

|

| undefined data. | |

TIR20: CRC32 Correct Byte Count LSB |

|

| ||

This register is the CRC32 Correct Byte | Count | |||

LSB register. |

|

|

|

|

Bit | Name | Reset Value | Description | |

|

|

|

|

|

C32C[7:0] | – | CRC32 Correct Count. The value in this register indicates the lower | ||

|

|

| 8 bits of the | |

|

|

| rect. CRC32 value 001h corresponds to the first byte of the received | |

message following the Start of Frame Delimiter. If the value in this register (and TIR21) does not match the length value indicated in the frame header (plus overhead for PHY and MAC headers and CRC) for frames that employ

Am79C930 | 99 |