P R E L I M I N A R Y | AMD |

|

|

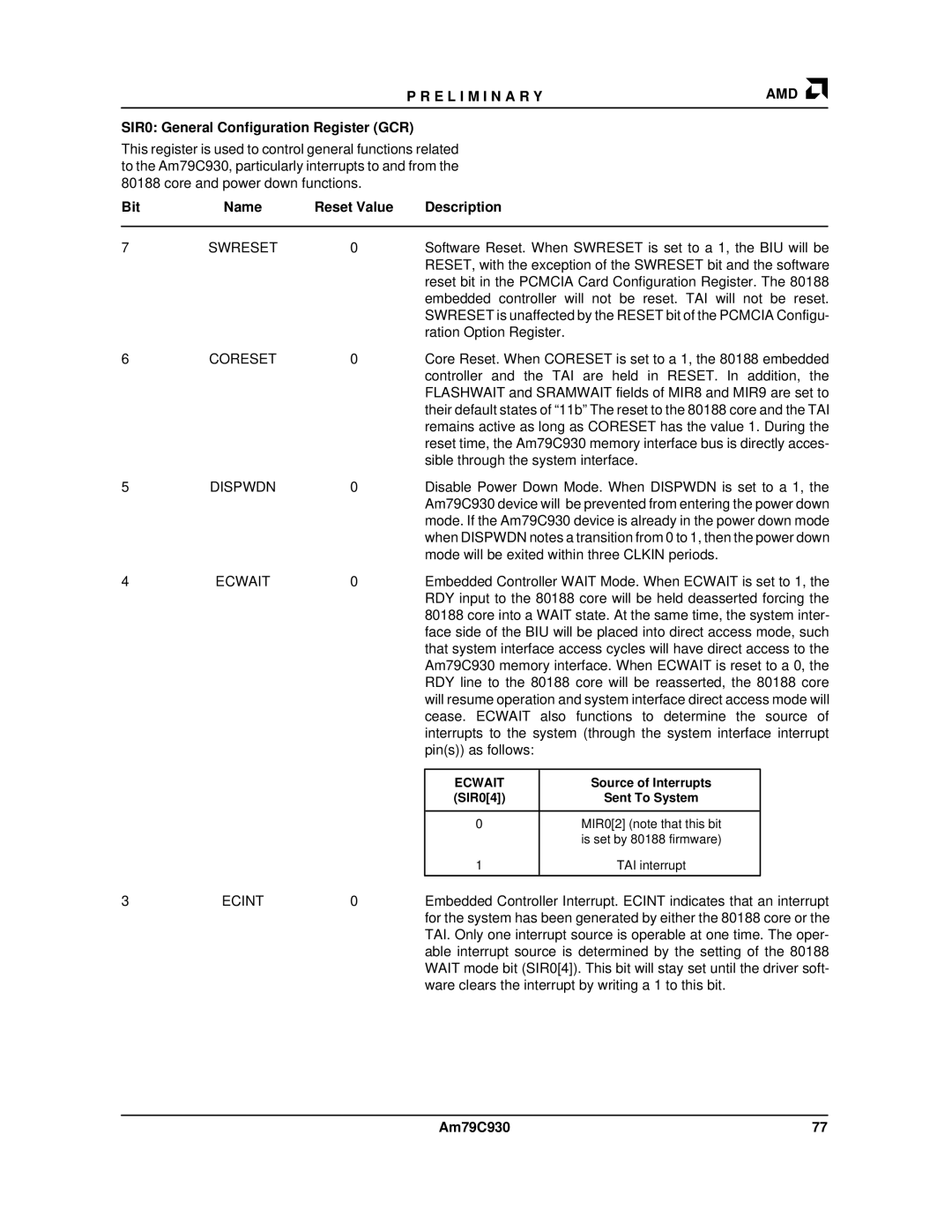

SIR0: General Configuration Register (GCR)

This register is used to control general functions related to the Am79C930, particularly interrupts to and from the 80188 core and power down functions.

Bit | Name | Reset Value | Description |

|

|

| |

|

|

|

|

|

|

| |

7 | SWRESET | 0 | Software Reset. When SWRESET is set to a 1, the BIU will be | ||||

|

|

| RESET, with the exception of the SWRESET bit and the software | ||||

|

|

| reset bit in the PCMCIA Card Configuration Register. The 80188 | ||||

|

|

| embedded controller will not be reset. TAI will not be reset. | ||||

|

|

| SWRESET is unaffected by the RESET bit of the PCMCIA Configu- | ||||

|

|

| ration Option Register. |

|

|

| |

6 | CORESET | 0 | Core Reset. When CORESET is set to a 1, the 80188 embedded | ||||

|

|

| controller and the TAI are held in RESET. In addition, the | ||||

|

|

| FLASHWAIT and SRAMWAIT fields of MIR8 and MIR9 are set to | ||||

|

|

| their default states of “11b” The reset to the 80188 core and the TAI | ||||

|

|

| remains active as long as CORESET has the value 1. During the | ||||

|

|

| reset time, the Am79C930 memory interface bus is directly acces- | ||||

|

|

| sible through the system interface. | ||||

5 | DISPWDN | 0 | Disable Power Down Mode. When DISPWDN is set to a 1, the | ||||

|

|

| Am79C930 device will be prevented from entering the power down | ||||

|

|

| mode. If the Am79C930 device is already in the power down mode | ||||

|

|

| when DISPWDN notes a transition from 0 to 1, then the power down | ||||

|

|

| mode will be exited within three CLKIN periods. | ||||

4 | ECWAIT | 0 | Embedded Controller WAIT Mode. When ECWAIT is set to 1, the | ||||

|

|

| RDY input to the 80188 core will be held deasserted forcing the | ||||

|

|

| 80188 core into a WAIT state. At the same time, the system inter- | ||||

|

|

| face side of the BIU will be placed into direct access mode, such | ||||

|

|

| that system interface access cycles will have direct access to the | ||||

|

|

| Am79C930 memory interface. When ECWAIT is reset to a 0, the | ||||

|

|

| RDY line to the 80188 core will be reasserted, the 80188 core | ||||

|

|

| will resume operation and system interface direct access mode will | ||||

|

|

| cease. ECWAIT also functions to determine the source of | ||||

|

|

| interrupts to the system (through the system interface interrupt | ||||

|

|

| pin(s)) as follows: |

|

|

| |

|

|

|

|

|

|

| |

|

|

| ECWAIT |

| Source of Interrupts |

|

|

|

|

| (SIR0[4]) |

| Sent To System |

| |

|

|

|

|

|

|

| |

|

|

| 0 |

| MIR0[2] (note that this bit |

|

|

|

|

|

|

| is set by 80188 firmware) |

| |

|

|

| 1 |

| TAI interrupt |

| |

|

|

|

|

|

|

|

|

3 | ECINT | 0 | Embedded Controller Interrupt. ECINT indicates that an interrupt | ||||

|

|

| for the system has been generated by either the 80188 core or the | ||||

TAI. Only one interrupt source is operable at one time. The oper- able interrupt source is determined by the setting of the 80188 WAIT mode bit (SIR0[4]). This bit will stay set until the driver soft- ware clears the interrupt by writing a 1 to this bit.

Am79C930 | 77 |