P R E L I M I N A R Y | AMD |

|

|

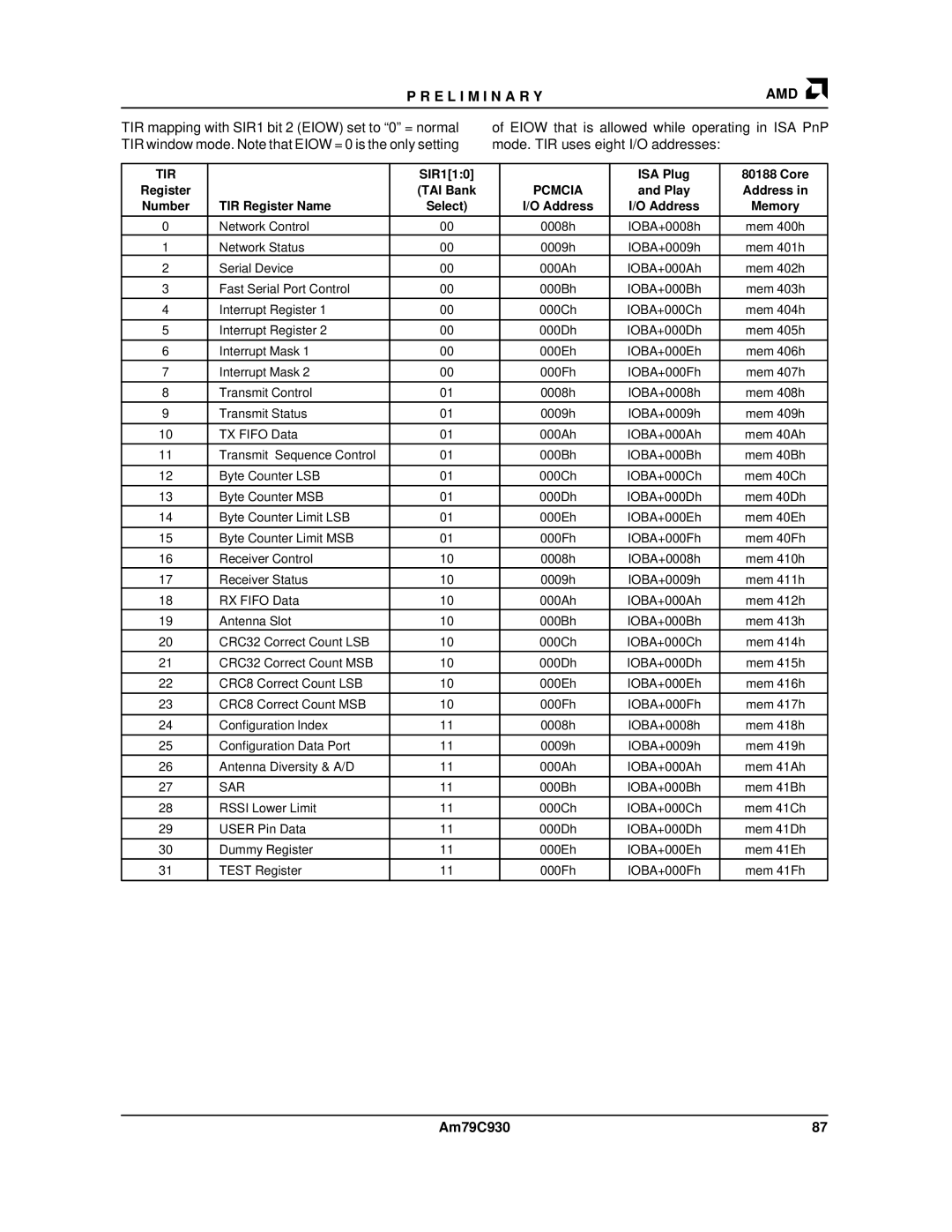

TIR mapping with SIR1 bit 2 (EIOW) set to “0” = normal TIR window mode. Note that EIOW = 0 is the only setting

of EIOW that is allowed while operating in ISA PnP mode. TIR uses eight I/O addresses:

TIR |

| SIR1[1:0] |

| ISA Plug | 80188 Core |

Register |

| (TAI Bank | PCMCIA | and Play | Address in |

Number | TIR Register Name | Select) | I/O Address | I/O Address | Memory |

|

|

|

|

|

|

0 | Network Control | 00 | 0008h | IOBA+0008h | mem 400h |

1 | Network Status | 00 | 0009h | IOBA+0009h | mem 401h |

2 | Serial Device | 00 | 000Ah | IOBA+000Ah | mem 402h |

3 | Fast Serial Port Control | 00 | 000Bh | IOBA+000Bh | mem 403h |

4 | Interrupt Register 1 | 00 | 000Ch | IOBA+000Ch | mem 404h |

|

|

|

|

|

|

5 | Interrupt Register 2 | 00 | 000Dh | IOBA+000Dh | mem 405h |

|

|

|

|

|

|

6 | Interrupt Mask 1 | 00 | 000Eh | IOBA+000Eh | mem 406h |

7 | Interrupt Mask 2 | 00 | 000Fh | IOBA+000Fh | mem 407h |

|

|

|

|

|

|

8 | Transmit Control | 01 | 0008h | IOBA+0008h | mem 408h |

9 | Transmit Status | 01 | 0009h | IOBA+0009h | mem 409h |

|

|

|

|

|

|

10 | TX FIFO Data | 01 | 000Ah | IOBA+000Ah | mem 40Ah |

|

|

|

|

|

|

11 | Transmit Sequence Control | 01 | 000Bh | IOBA+000Bh | mem 40Bh |

|

|

|

|

|

|

12 | Byte Counter LSB | 01 | 000Ch | IOBA+000Ch | mem 40Ch |

|

|

|

|

|

|

13 | Byte Counter MSB | 01 | 000Dh | IOBA+000Dh | mem 40Dh |

14 | Byte Counter Limit LSB | 01 | 000Eh | IOBA+000Eh | mem 40Eh |

15 | Byte Counter Limit MSB | 01 | 000Fh | IOBA+000Fh | mem 40Fh |

|

|

|

|

|

|

16 | Receiver Control | 10 | 0008h | IOBA+0008h | mem 410h |

17 | Receiver Status | 10 | 0009h | IOBA+0009h | mem 411h |

18 | RX FIFO Data | 10 | 000Ah | IOBA+000Ah | mem 412h |

19 | Antenna Slot | 10 | 000Bh | IOBA+000Bh | mem 413h |

20 | CRC32 Correct Count LSB | 10 | 000Ch | IOBA+000Ch | mem 414h |

|

|

|

|

|

|

21 | CRC32 Correct Count MSB | 10 | 000Dh | IOBA+000Dh | mem 415h |

|

|

|

|

|

|

22 | CRC8 Correct Count LSB | 10 | 000Eh | IOBA+000Eh | mem 416h |

|

|

|

|

|

|

23 | CRC8 Correct Count MSB | 10 | 000Fh | IOBA+000Fh | mem 417h |

|

|

|

|

|

|

24 | Configuration Index | 11 | 0008h | IOBA+0008h | mem 418h |

25 | Configuration Data Port | 11 | 0009h | IOBA+0009h | mem 419h |

|

|

|

|

|

|

26 | Antenna Diversity & A/D | 11 | 000Ah | IOBA+000Ah | mem 41Ah |

|

|

|

|

|

|

27 | SAR | 11 | 000Bh | IOBA+000Bh | mem 41Bh |

|

|

|

|

|

|

28 | RSSI Lower Limit | 11 | 000Ch | IOBA+000Ch | mem 41Ch |

|

|

|

|

|

|

29 | USER Pin Data | 11 | 000Dh | IOBA+000Dh | mem 41Dh |

30 | Dummy Register | 11 | 000Eh | IOBA+000Eh | mem 41Eh |

31 | TEST Register | 11 | 000Fh | IOBA+000Fh | mem 41Fh |

|

|

|

|

|

|

Am79C930 | 87 |