P R E L I M I N A R Y | AMD |

|

|

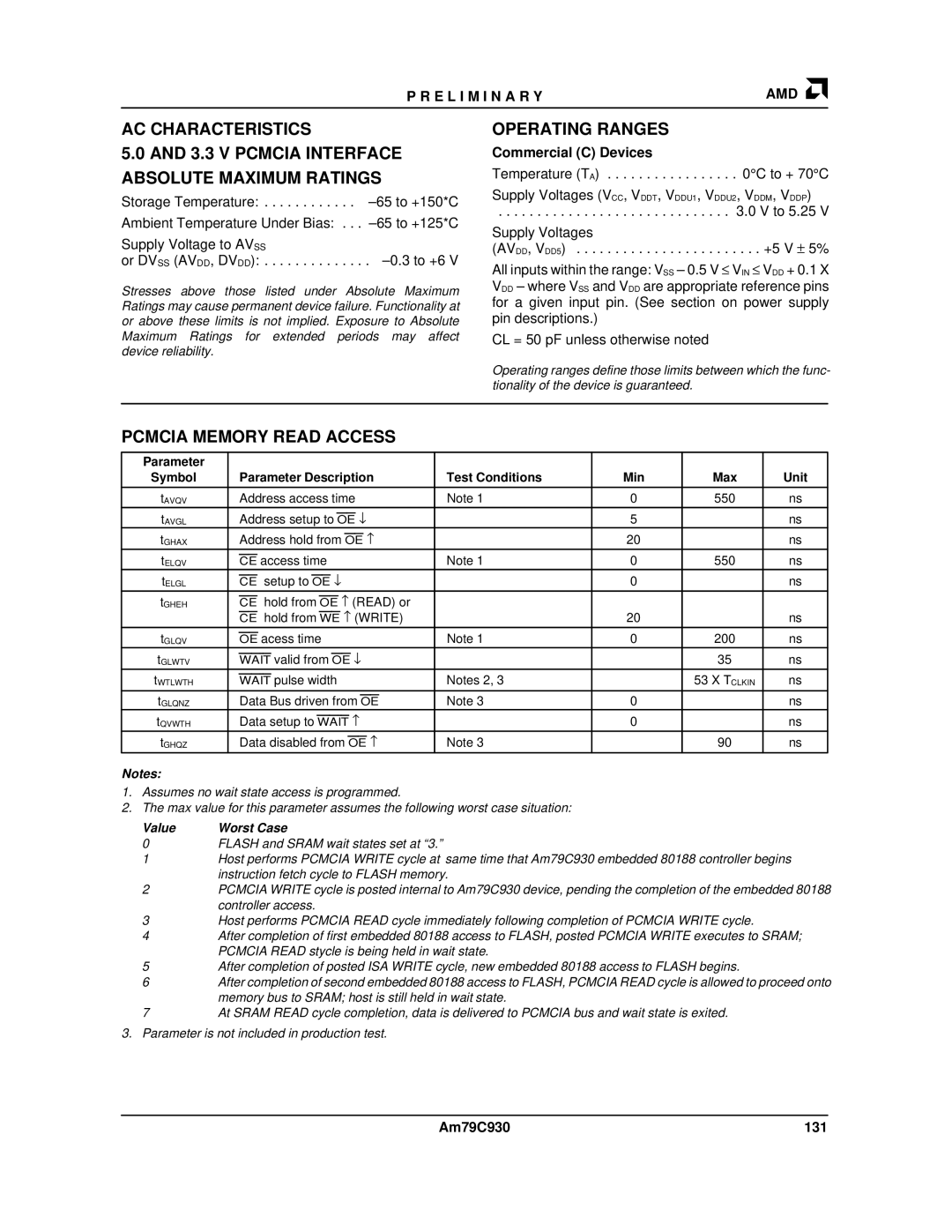

AC CHARACTERISTICS

5.0AND 3.3 V PCMCIA INTERFACE ABSOLUTE MAXIMUM RATINGS

Storage Temperature: . . . . . . . . . . . .

Ambient Temperature Under Bias: . . .

Supply Voltage to AVSS

or DVSS (AVDD, DVDD): . . . . . . . . . . . . . .

Stresses above those listed under Absolute Maximum Ratings may cause permanent device failure. Functionality at or above these limits is not implied. Exposure to Absolute Maximum Ratings for extended periods may affect device reliability.

OPERATING RANGES

Commercial (C) Devices

Temperature (TA) . . . . . . . . . . . . . . . . . 0°C to + 70°C

Supply Voltages (VCC, VDDT, VDDU1, VDDU2, VDDM, VDDP)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3.0 V to 5.25 V

Supply Voltages

(AVDD, VDD5) . . . . . . . . . . . . . . . . . . . . . . . . +5 V ± 5%

All inputs within the range: VSS – 0.5 V ≤ VIN ≤ VDD + 0.1 X VDD – where V SS and VDD are appropriate reference pins for a given input pin. (See section on power supply pin descriptions.)

CL = 50 pF unless otherwise noted

Operating ranges define those limits between which the func- tionality of the device is guaranteed.

PCMCIA MEMORY READ ACCESS

Parameter |

|

|

|

|

|

Symbol | Parameter Description | Test Conditions | Min | Max | Unit |

|

|

|

|

|

|

tAVQV | Address access time | Note 1 | 0 | 550 | ns |

tAVGL | Address setup to OE ↓ |

| 5 |

| ns |

tGHAX | Address hold from OE − |

| 20 |

| ns |

tELQV | CE access time | Note 1 | 0 | 550 | ns |

tELGL | CE setup to OE ↓ |

| 0 |

| ns |

|

|

|

|

|

|

tGHEH | CE hold from OE − (READ) or |

|

|

|

|

| CE hold from WE − (WRITE) |

| 20 |

| ns |

tGLQV | OE acess time | Note 1 | 0 | 200 | ns |

tGLWTV | WAIT valid from OE ↓ |

|

| 35 | ns |

|

|

|

|

|

|

tWTLWTH | WAIT pulse width | Notes 2, 3 |

| 53 X TCLKIN | ns |

|

|

|

|

|

|

tGLQNZ | Data Bus driven from OE | Note 3 | 0 |

| ns |

tQVWTH | Data setup to WAIT − |

| 0 |

| ns |

tGHQZ | Data disabled from OE − | Note 3 |

| 90 | ns |

|

|

|

|

|

|

Notes:

1.Assumes no wait state access is programmed.

2.The max value for this parameter assumes the following worst case situation:

Value | Worst Case |

0FLASH and SRAM wait states set at “3.”

1Host performs PCMCIA WRITE cycle at same time that Am79C930 embedded 80188 controller begins instruction fetch cycle to FLASH memory.

2PCMCIA WRITE cycle is posted internal to Am79C930 device, pending the completion of the embedded 80188 controller access.

3Host performs PCMCIA READ cycle immediately following completion of PCMCIA WRITE cycle.

4After completion of first embedded 80188 access to FLASH, posted PCMCIA WRITE executes to SRAM; PCMCIA READ stycle is being held in wait state.

5After completion of posted ISA WRITE cycle, new embedded 80188 access to FLASH begins.

6After completion of second embedded 80188 access to FLASH, PCMCIA READ cycle is allowed to proceed onto memory bus to SRAM; host is still held in wait state.

7At SRAM READ cycle completion, data is delivered to PCMCIA bus and wait state is exited.

3.Parameter is not included in production test.

Am79C930 | 131 |