|

|

| P R E L I M I N A R Y | AMD | |

|

|

|

|

| |

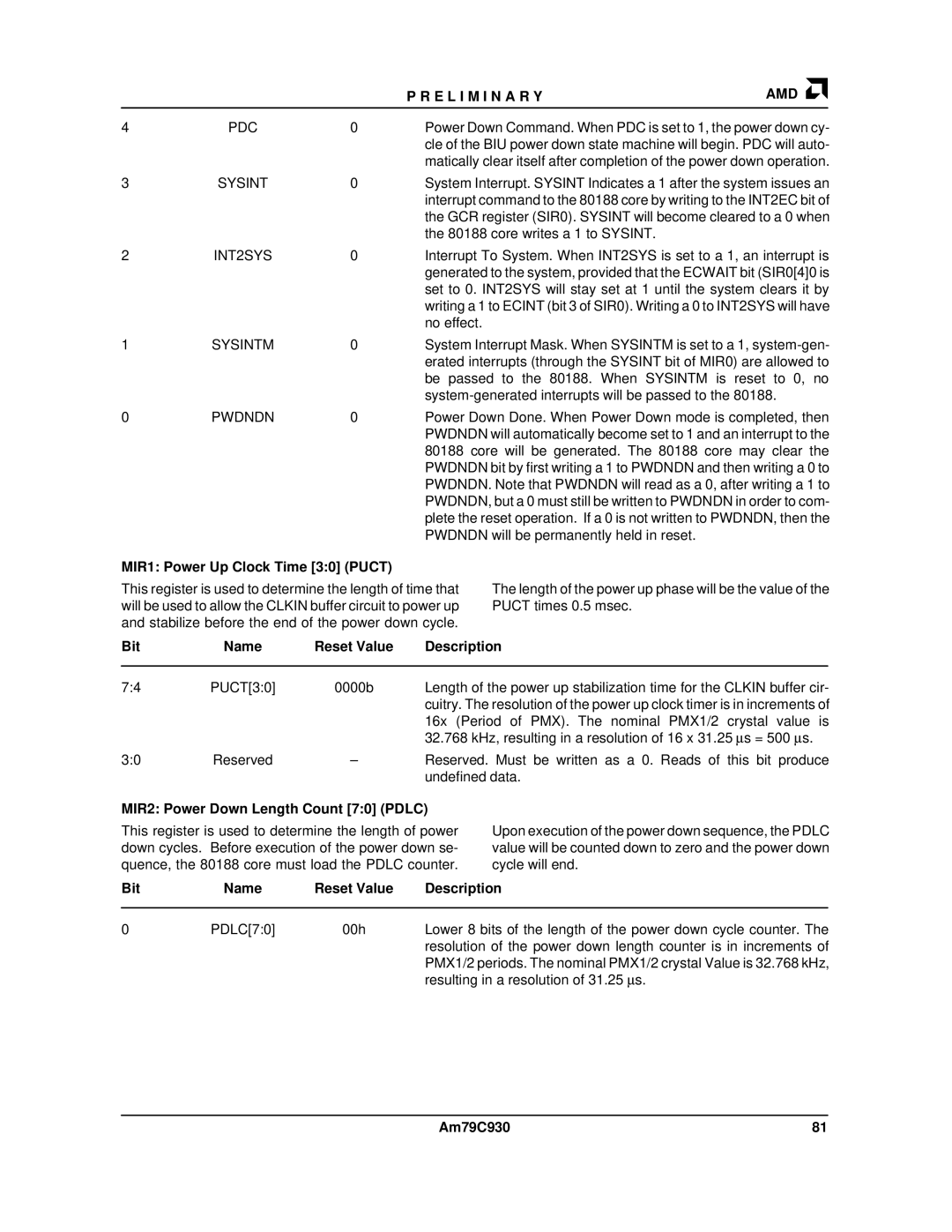

4 | PDC | 0 | Power Down Command. When PDC is set to 1, the power down cy- | ||

|

|

| cle of the BIU power down state machine will begin. PDC will auto- | ||

|

|

| matically clear itself after completion of the power down operation. | ||

3 | SYSINT | 0 | System Interrupt. SYSINT Indicates a 1 after the system issues an | ||

|

|

| interrupt command to the 80188 core by writing to the INT2EC bit of | ||

|

|

| the GCR register (SIR0). SYSINT will become cleared to a 0 when | ||

|

|

| the 80188 core writes a 1 to SYSINT. |

|

|

2 | INT2SYS | 0 | Interrupt To System. When INT2SYS is set to a 1, an interrupt is | ||

|

|

| generated to the system, provided that the ECWAIT bit (SIR0[4]0 is | ||

|

|

| set to 0. INT2SYS will stay set at 1 until the system clears it by | ||

|

|

| writing a 1 to ECINT (bit 3 of SIR0). Writing a 0 to INT2SYS will have | ||

|

|

| no effect. |

|

|

1 | SYSINTM | 0 | System Interrupt Mask. When SYSINTM is set to a 1, | ||

|

|

| erated interrupts (through the SYSINT bit of MIR0) are allowed to | ||

|

|

| be passed to the 80188. When SYSINTM is reset to 0, no | ||

|

|

|

| ||

0 | PWDNDN | 0 | Power Down Done. When Power Down mode is completed, then | ||

|

|

| PWDNDN will automatically become set to 1 and an interrupt to the | ||

|

|

| 80188 core will be generated. The 80188 core may clear the | ||

|

|

| PWDNDN bit by first writing a 1 to PWDNDN and then writing a 0 to | ||

|

|

| PWDNDN. Note that PWDNDN will read as a 0, after writing a 1 to | ||

|

|

| PWDNDN, but a 0 must still be written to PWDNDN in order to com- | ||

|

|

| plete the reset operation. If a 0 is not written to PWDNDN, then the | ||

|

|

| PWDNDN will be permanently held in reset. |

|

|

MIR1: Power Up Clock Time [3:0] (PUCT)

This register is used to determine the length of time that will be used to allow the CLKIN buffer circuit to power up and stabilize before the end of the power down cycle.

The length of the power up phase will be the value of the PUCT times 0.5 msec.

Bit | Name | Reset Value | Description | |

|

|

|

|

|

7:4 | PUCT[3:0] | 0000b | Length of the power up stabilization time for the CLKIN buffer cir- | |

|

|

| cuitry. The resolution of the power up clock timer is in increments of | |

|

|

| 16x (Period of PMX). The nominal PMX1/2 crystal value is | |

|

|

| 32.768 kHz, resulting in a resolution of 16 x 31.25 μs = 500 μs. | |

3:0 | Reserved | – | Reserved. Must be written as a 0. Reads of this bit produce | |

|

|

| undefined data. | |

MIR2: Power Down Length Count [7:0] (PDLC)

This register is used to determine the length of power down cycles. Before execution of the power down se- quence, the 80188 core must load the PDLC counter.

Upon execution of the power down sequence, the PDLC value will be counted down to zero and the power down cycle will end.

Bit | Name | Reset Value | Description | |

|

|

|

|

|

0 | PDLC[7:0] | 00h | Lower 8 bits of the length of the power down cycle counter. The | |

|

|

| resolution of the power down length counter is in increments of | |

|

|

| PMX1/2 periods. The nominal PMX1/2 crystal Value is 32.768 kHz, | |

|

|

| resulting in a resolution of 31.25 μs. | |

Am79C930 | 81 |