AMD | P R E L I M I N A R Y |

|

|

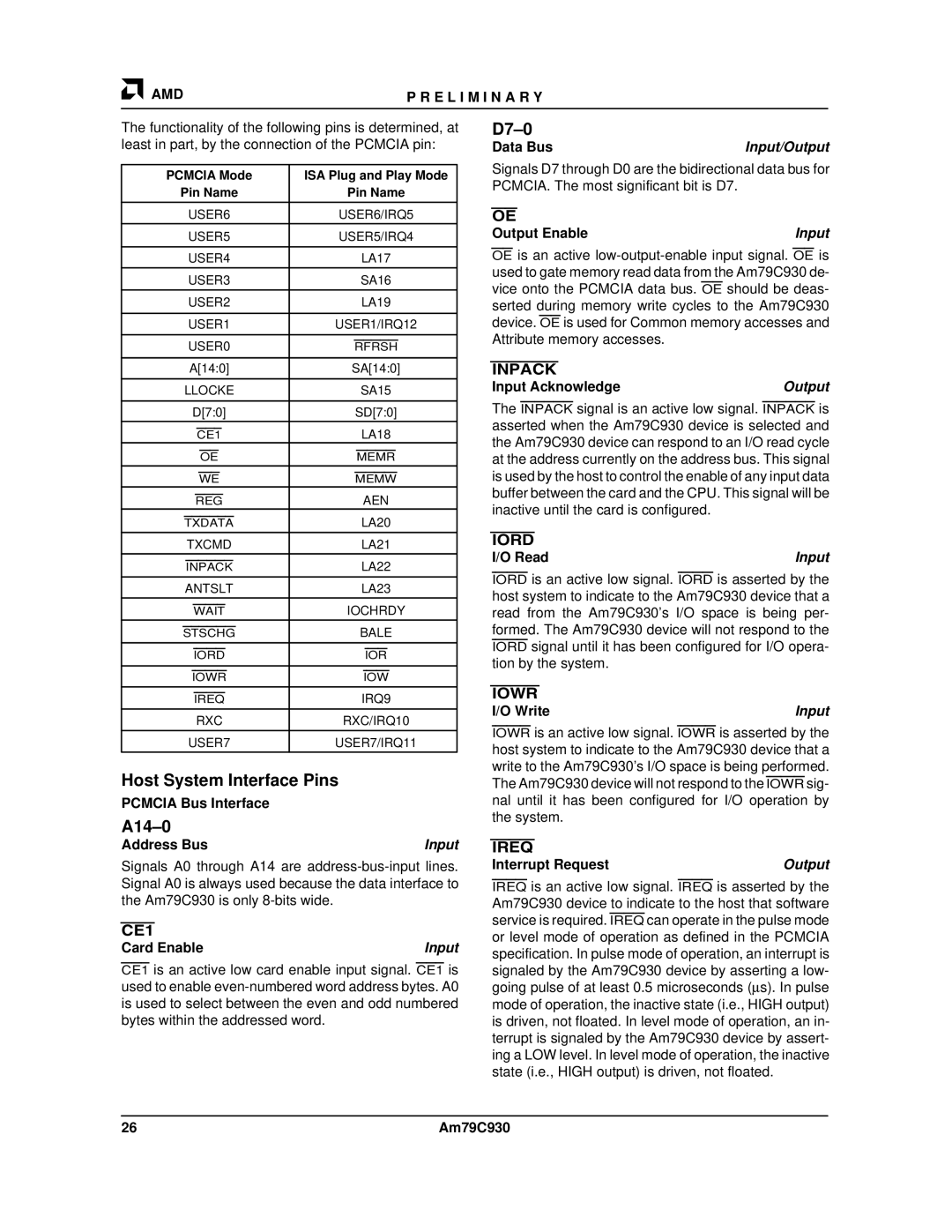

The functionality of the following pins is determined, at least in part, by the connection of the PCMCIA pin:

PCMCIA Mode | ISA Plug and Play Mode |

Pin Name | Pin Name |

|

|

USER6 | USER6/IRQ5 |

USER5 | USER5/IRQ4 |

|

|

USER4 | LA17 |

USER3 | SA16 |

|

|

USER2 | LA19 |

|

|

USER1 | USER1/IRQ12 |

|

|

USER0 | RFRSH |

|

|

A[14:0] | SA[14:0] |

|

|

LLOCKE | SA15 |

|

|

D[7:0] | SD[7:0] |

CE1 | LA18 |

OE | MEMR |

|

|

WE | MEMW |

REG | AEN |

TXDATA | LA20 |

|

|

TXCMD | LA21 |

INPACK | LA22 |

|

|

ANTSLT | LA23 |

WAIT | IOCHRDY |

|

|

STSCHG | BALE |

|

|

IORD | IOR |

|

|

IOWR | IOW |

|

|

IREQ | IRQ9 |

|

|

RXC | RXC/IRQ10 |

|

|

USER7 | USER7/IRQ11 |

Host System Interface Pins

PCMCIA Bus Interface

A14–0

Address Bus | Input |

Signals A0 through A14 are

CE1

Card Enable | Input |

CE1 is an active low card enable input signal. CE1 is used to enable

D7–0

Data Bus | Input/Output |

Signals D7 through D0 are the bidirectional data bus for PCMCIA. The most significant bit is D7.

OE

Output Enable | Input |

OE is an active

INPACK

Input Acknowledge | Output |

The INPACK signal is an active low signal. INPACK is asserted when the Am79C930 device is selected and the Am79C930 device can respond to an I/O read cycle at the address currently on the address bus. This signal is used by the host to control the enable of any input data buffer between the card and the CPU. This signal will be inactive until the card is configured.

IORD

I/O Read | Input |

IORD is an active low signal. IORD is asserted by the host system to indicate to the Am79C930 device that a read from the Am79C930's I/O space is being per- formed. The Am79C930 device will not respond to the IORD signal until it has been configured for I/O opera- tion by the system.

IOWR

I/O Write | Input |

IOWR is an active low signal. IOWR is asserted by the host system to indicate to the Am79C930 device that a write to the Am79C930's I/O space is being performed. The Am79C930 device will not respond to the IOWR sig- nal until it has been configured for I/O operation by the system.

IREQ

Interrupt Request | Output |

IREQ is an active low signal. IREQ is asserted by the Am79C930 device to indicate to the host that software service is required. IREQ can operate in the pulse mode or level mode of operation as defined in the PCMCIA specification. In pulse mode of operation, an interrupt is signaled by the Am79C930 device by asserting a low- going pulse of at least 0.5 microseconds (μs). In pulse mode of operation, the inactive state (i.e., HIGH output) is driven, not floated. In level mode of operation, an in- terrupt is signaled by the Am79C930 device by assert- ing a LOW level. In level mode of operation, the inactive state (i.e., HIGH output) is driven, not floated.

26 | Am79C930 |