AMDP R E L I M I N A R Y

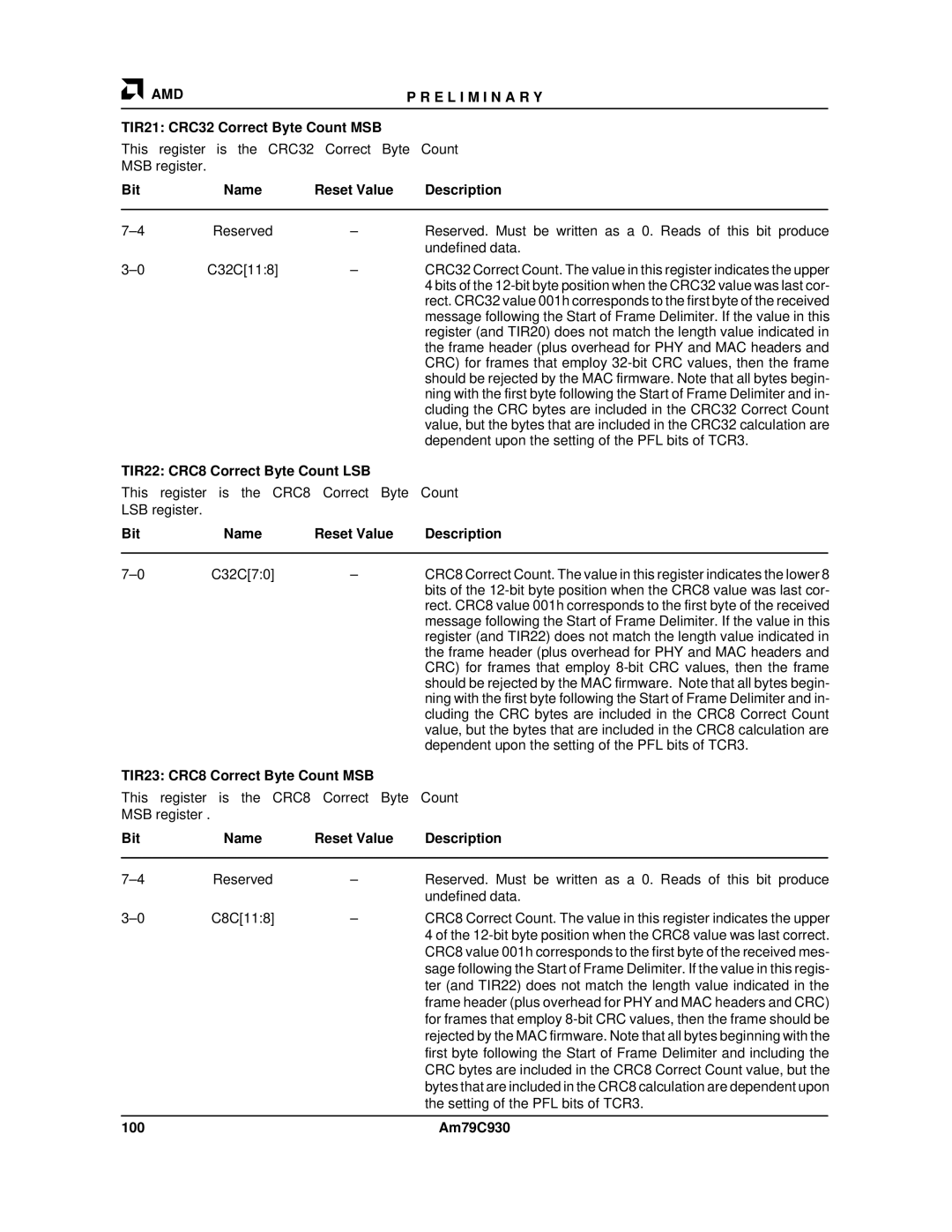

TIR21: CRC32 Correct Byte Count MSB

This register is the CRC32 Correct Byte Count

MSB register.

Bit | Name | Reset Value | Description | ||

|

|

|

|

|

|

Reserved | – |

| Reserved. Must be written as a 0. Reads of this bit produce | ||

|

|

|

| undefined data. | |

C32C[11:8] | – |

| CRC32 Correct Count. The value in this register indicates the upper | ||

|

|

|

| 4 bits of the | |

|

|

|

| rect. CRC32 value 001h corresponds to the first byte of the received | |

|

|

|

| message following the Start of Frame Delimiter. If the value in this | |

|

|

|

| register (and TIR20) does not match the length value indicated in | |

|

|

|

| the frame header (plus overhead for PHY and MAC headers and | |

|

|

|

| CRC) for frames that employ | |

|

|

|

| should be rejected by the MAC firmware. Note that all bytes begin- | |

|

|

|

| ning with the first byte following the Start of Frame Delimiter and in- | |

|

|

|

| cluding the CRC bytes are included in the CRC32 Correct Count | |

|

|

|

| value, but the bytes that are included in the CRC32 calculation are | |

|

|

|

| dependent upon the setting of the PFL bits of TCR3. | |

TIR22: CRC8 Correct Byte Count LSB |

|

|

| ||

This register is the CRC8 | Correct | Byte | Count | ||

LSB register. |

|

|

|

|

|

Bit | Name | Reset Value | Description | ||

|

|

|

|

|

|

C32C[7:0] | – |

| CRC8 Correct Count. The value in this register indicates the lower 8 | ||

|

|

|

| bits of the | |

|

|

|

| rect. CRC8 value 001h corresponds to the first byte of the received | |

|

|

|

| message following the Start of Frame Delimiter. If the value in this | |

|

|

|

| register (and TIR22) does not match the length value indicated in | |

|

|

|

| the frame header (plus overhead for PHY and MAC headers and | |

|

|

|

| CRC) for frames that employ | |

|

|

|

| should be rejected by the MAC firmware. Note that all bytes begin- | |

|

|

|

| ning with the first byte following the Start of Frame Delimiter and in- | |

|

|

|

| cluding the CRC bytes are included in the CRC8 Correct Count | |

|

|

|

| value, but the bytes that are included in the CRC8 calculation are | |

|

|

|

| dependent upon the setting of the PFL bits of TCR3. | |

TIR23: CRC8 Correct Byte Count MSB |

|

|

| ||

This register is the CRC8 | Correct | Byte | Count | ||

MSB register . |

|

|

|

| |

Bit | Name | Reset Value | Description | ||

|

|

|

|

|

|

Reserved | – |

| Reserved. Must be written as a 0. Reads of this bit produce | ||

|

|

|

| undefined data. | |

C8C[11:8] | – |

| CRC8 Correct Count. The value in this register indicates the upper | ||

|

|

|

| 4 of the | |

|

|

|

| CRC8 value 001h corresponds to the first byte of the received mes- | |

|

|

|

| sage following the Start of Frame Delimiter. If the value in this regis- | |

|

|

|

| ter (and TIR22) does not match the length value indicated in the | |

|

|

|

| frame header (plus overhead for PHY and MAC headers and CRC) | |

|

|

|

| for frames that employ | |

|

|

|

| rejected by the MAC firmware. Note that all bytes beginning with the | |

|

|

|

| first byte following the Start of Frame Delimiter and including the | |

|

|

|

| CRC bytes are included in the CRC8 Correct Count value, but the | |

|

|

|

| bytes that are included in the CRC8 calculation are dependent upon | |

|

|

|

| the setting of the PFL bits of TCR3. | |

|

|

|

|

|

|

100 |

|

|

| Am79C930 | |