P R E L I M I N A R Y | AMD | ||

|

|

|

|

|

|

|

|

|

|

| Programmed |

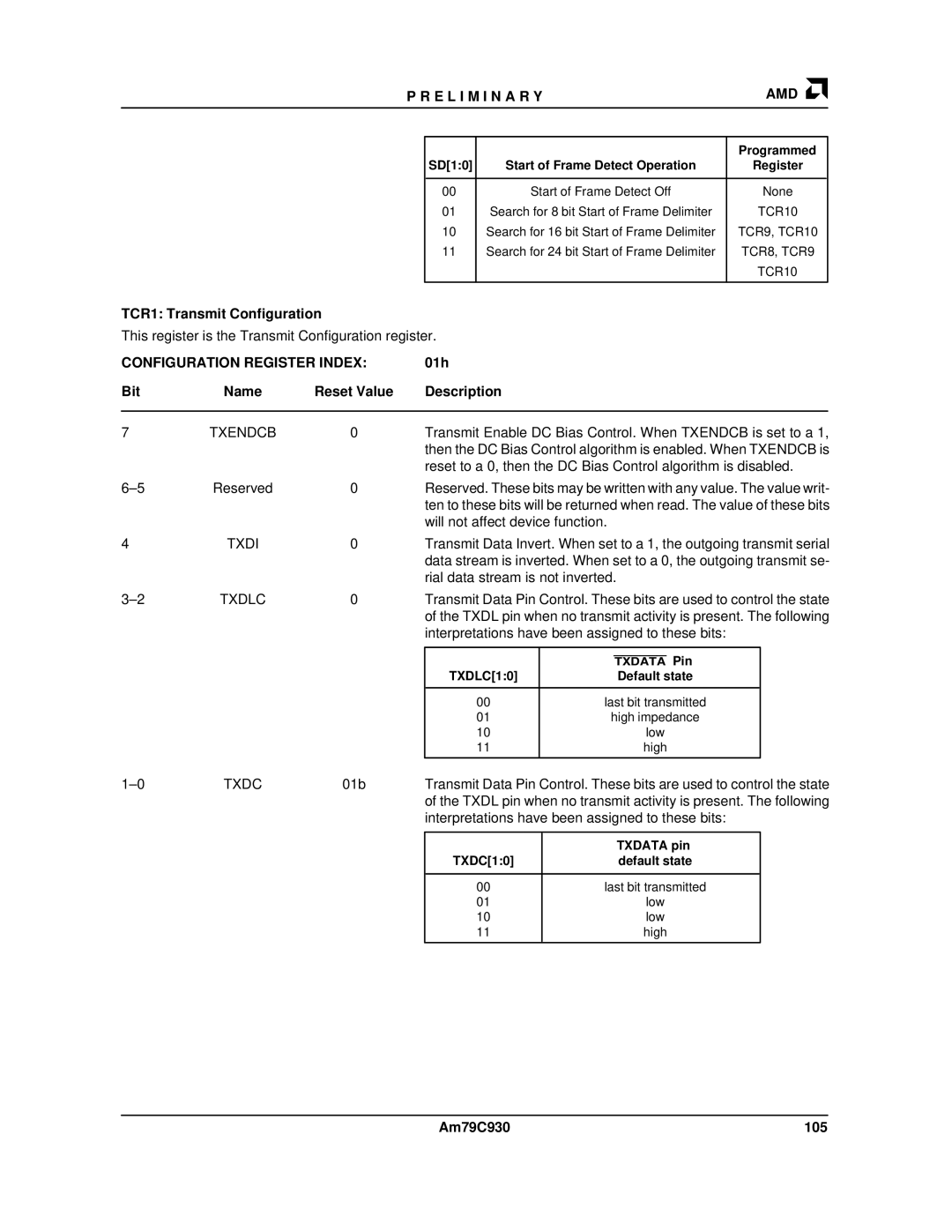

| SD[1:0] | Start of Frame Detect Operation | Register |

|

|

|

|

| 00 | Start of Frame Detect Off | None |

| 01 | Search for 8 bit Start of Frame Delimiter | TCR10 |

| 10 | Search for 16 bit Start of Frame Delimiter | TCR9, TCR10 |

| 11 | Search for 24 bit Start of Frame Delimiter | TCR8, TCR9 |

|

|

| TCR10 |

|

|

|

|

TCR1: Transmit Configuration

This register is the Transmit Configuration register.

CONFIGURATION REGISTER INDEX: |

| 01h |

|

|

| ||

Bit | Name | Reset Value |

| Description |

|

|

|

|

|

|

|

|

|

|

|

7 | TXENDCB | 0 |

| Transmit Enable DC Bias Control. When TXENDCB is set to a 1, | |||

|

|

|

| then the DC Bias Control algorithm is enabled. When TXENDCB is | |||

|

|

|

| reset to a 0, then the DC Bias Control algorithm is disabled. | |||

Reserved | 0 | Reserved. These bits may be written with any value. The value writ- | |||||

|

|

|

| ten to these bits will be returned when read. The value of these bits | |||

|

|

|

| will not affect device function. | |||

4 | TXDI | 0 |

| Transmit Data Invert. When set to a 1, the outgoing transmit serial | |||

|

|

|

| data stream is inverted. When set to a 0, the outgoing transmit se- | |||

|

|

|

| rial data stream is not inverted. | |||

TXDLC | 0 | Transmit Data Pin Control. These bits are used to control the state | |||||

|

|

|

| of the TXDL pin when no transmit activity is present. The following | |||

|

|

|

| interpretations have been assigned to these bits: | |||

|

|

|

|

|

|

| |

|

|

|

|

| TXDATA Pin |

| |

|

|

|

| TXDLC[1:0] | Default state |

| |

|

|

|

|

|

|

| |

|

|

|

| 00 | last bit transmitted |

|

|

|

|

|

| 01 | high impedance |

| |

|

|

|

| 10 | low |

| |

|

|

|

| 11 | high |

| |

|

|

|

|

|

|

|

|

TXDC | 01b | Transmit Data Pin Control. These bits are used to control the state | |||||

|

|

|

| of the TXDL pin when no transmit activity is present. The following | |||

|

|

|

| interpretations have been assigned to these bits: | |||

|

|

|

|

|

| ||

|

|

|

|

| TXDATA pin |

|

|

|

|

|

| TXDC[1:0] | default state |

| |

|

|

|

|

|

|

| |

|

|

|

| 00 | last bit transmitted |

|

|

|

|

|

| 01 | low |

| |

|

|

|

| 10 | low |

| |

|

|

|

| 11 | high |

| |

|

|

|

|

|

|

|

|

Am79C930 | 105 |