P R E L I M I N A R Y | AMD |

|

|

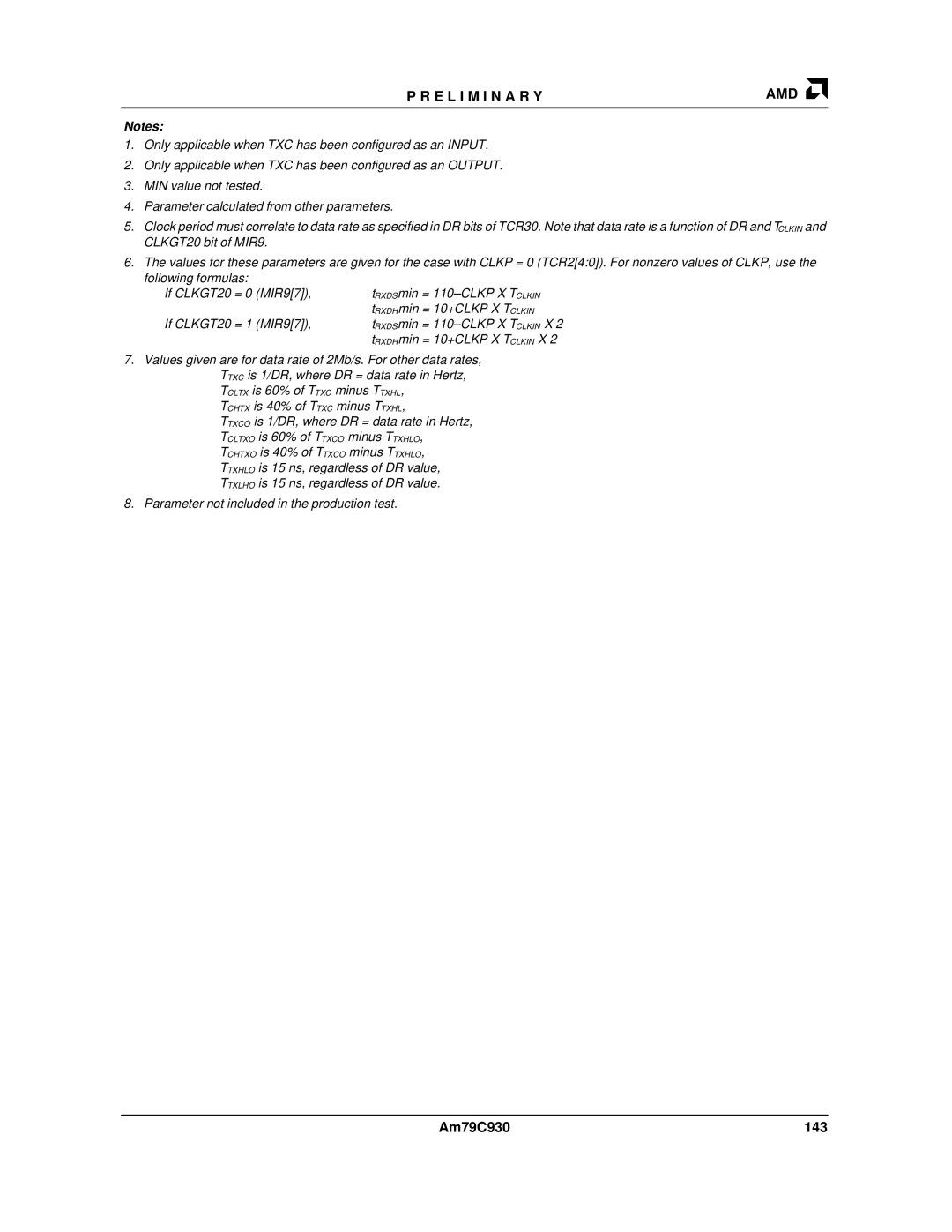

Notes:

1.Only applicable when TXC has been configured as an INPUT.

2.Only applicable when TXC has been configured as an OUTPUT.

3.MIN value not tested.

4.Parameter calculated from other parameters.

5.Clock period must correlate to data rate as specified in DR bits of TCR30. Note that data rate is a function of DR and TCLKIN and CLKGT20 bit of MIR9.

6.The values for these parameters are given for the case with CLKP = 0 (TCR2[4:0]). For nonzero values of CLKP, use the

following formulas:

If CLKGT20 = 0 (MIR9[7]),

If CLKGT20 = 1 (MIR9[7]),

7.Values given are for data rate of 2Mb/s. For other data rates, TTXC is 1/DR, where DR = data rate in Hertz, TCLTX is 60% of TTXC minus TTXHL,

TCHTX is 40% of TTXC minus TTXHL,

TTXCO is 1/DR, where DR = data rate in Hertz, TCLTXO is 60% of TTXCO minus TTXHLO, TCHTXO is 40% of TTXCO minus TTXHLO, TTXHLO is 15 ns, regardless of DR value, TTXLHO is 15 ns, regardless of DR value.

8.Parameter not included in the production test.

Am79C930 | 143 |