|

|

| P R E L I M I N A R Y | AMD | ||

|

|

|

|

| ||

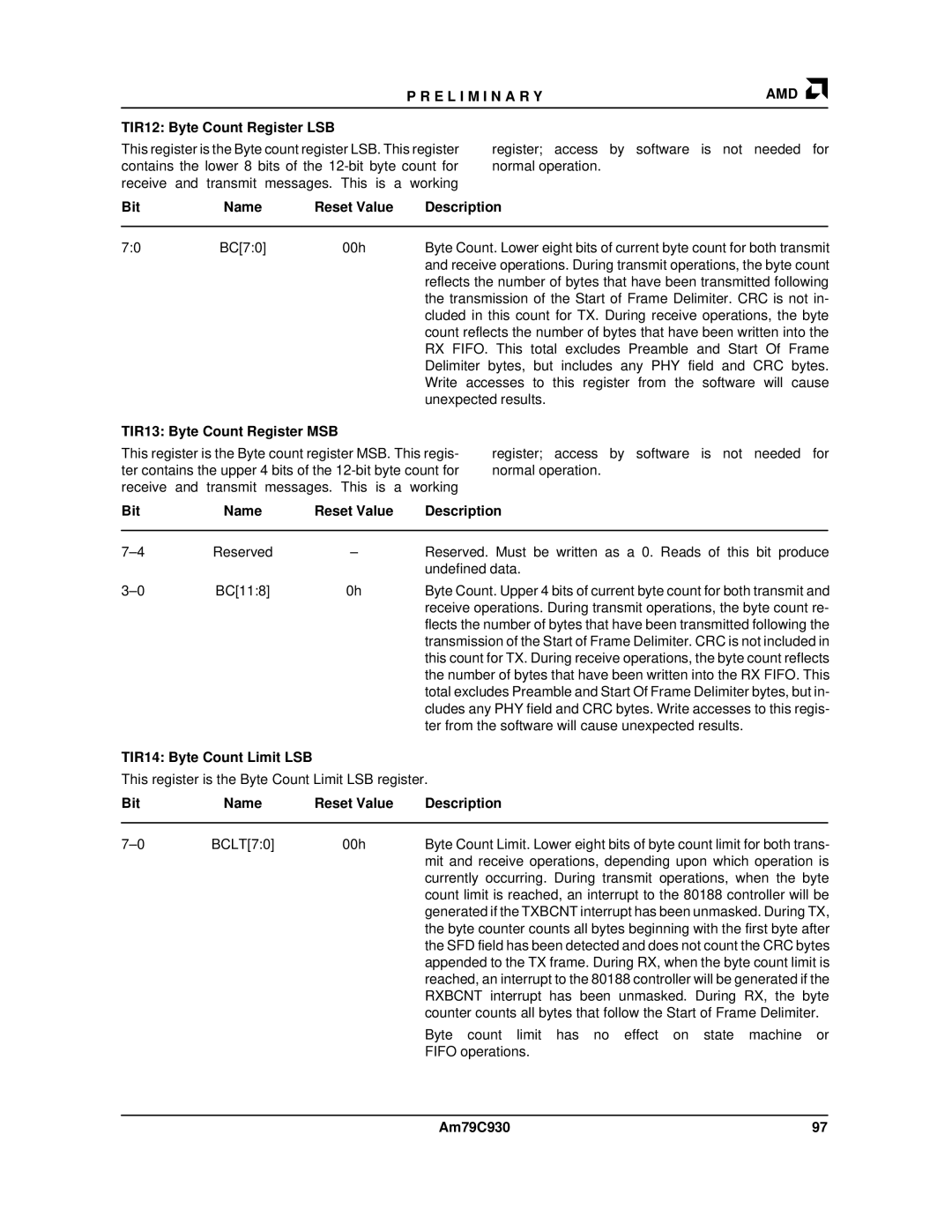

TIR12: Byte Count Register LSB |

|

|

|

| ||

This register is the Byte count register LSB. This register | register; access by software is not needed for | |||||

contains the lower 8 bits of the | normal operation. |

|

| |||

receive and transmit messages. This is a working |

|

|

| |||

Bit | Name | Reset Value | Description |

|

| |

|

|

|

|

| ||

7:0 | BC[7:0] | 00h | Byte Count. Lower eight bits of current byte count for both transmit | |||

|

|

| and receive operations. During transmit operations, the byte count | |||

|

|

| reflects the number of bytes that have been transmitted following | |||

|

|

| the transmission of the Start of Frame Delimiter. CRC is not in- | |||

|

|

| cluded in this count for TX. During receive operations, the byte | |||

|

|

| count reflects the number of bytes that have been written into the | |||

|

|

| RX FIFO. This total excludes Preamble and Start Of Frame | |||

|

|

| Delimiter bytes, but includes any PHY field and CRC bytes. | |||

|

|

| Write accesses to this register from the software will cause | |||

|

|

| unexpected results. |

|

| |

TIR13: Byte Count Register MSB |

|

|

|

| ||

This register is the Byte count register MSB. This regis- | register; access by software is not needed for | |||||

ter contains the upper 4 bits of the | normal operation. |

|

| |||

receive | and transmit messages. This is a | working |

|

|

| |

Bit | Name | Reset Value | Description |

|

|

|

|

Reserved | – | Reserved. Must be written as a 0. Reads of this bit produce | |

|

|

| undefined data. |

BC[11:8] | 0h | Byte Count. Upper 4 bits of current byte count for both transmit and |

receive operations. During transmit operations, the byte count re- flects the number of bytes that have been transmitted following the transmission of the Start of Frame Delimiter. CRC is not included in this count for TX. During receive operations, the byte count reflects the number of bytes that have been written into the RX FIFO. This total excludes Preamble and Start Of Frame Delimiter bytes, but in- cludes any PHY field and CRC bytes. Write accesses to this regis- ter from the software will cause unexpected results.

TIR14: Byte Count Limit LSB

This register is the Byte Count Limit LSB register.

Bit | Name | Reset Value | Description | |

|

|

|

|

|

BCLT[7:0] | 00h | Byte Count Limit. Lower eight bits of byte count limit for both trans- | ||

|

|

| mit and receive operations, depending upon which operation is | |

|

|

| currently occurring. During transmit operations, when the byte | |

|

|

| count limit is reached, an interrupt to the 80188 controller will be | |

|

|

| generated if the TXBCNT interrupt has been unmasked. During TX, | |

|

|

| the byte counter counts all bytes beginning with the first byte after | |

|

|

| the SFD field has been detected and does not count the CRC bytes | |

|

|

| appended to the TX frame. During RX, when the byte count limit is | |

|

|

| reached, an interrupt to the 80188 controller will be generated if the | |

|

|

| RXBCNT interrupt has been unmasked. During RX, the byte | |

|

|

| counter counts all bytes that follow the Start of Frame Delimiter. | |

|

|

| Byte count limit has no effect on state machine or | |

|

|

| FIFO operations. | |

Am79C930 | 97 |