AMDP R E L I M I N A R Y

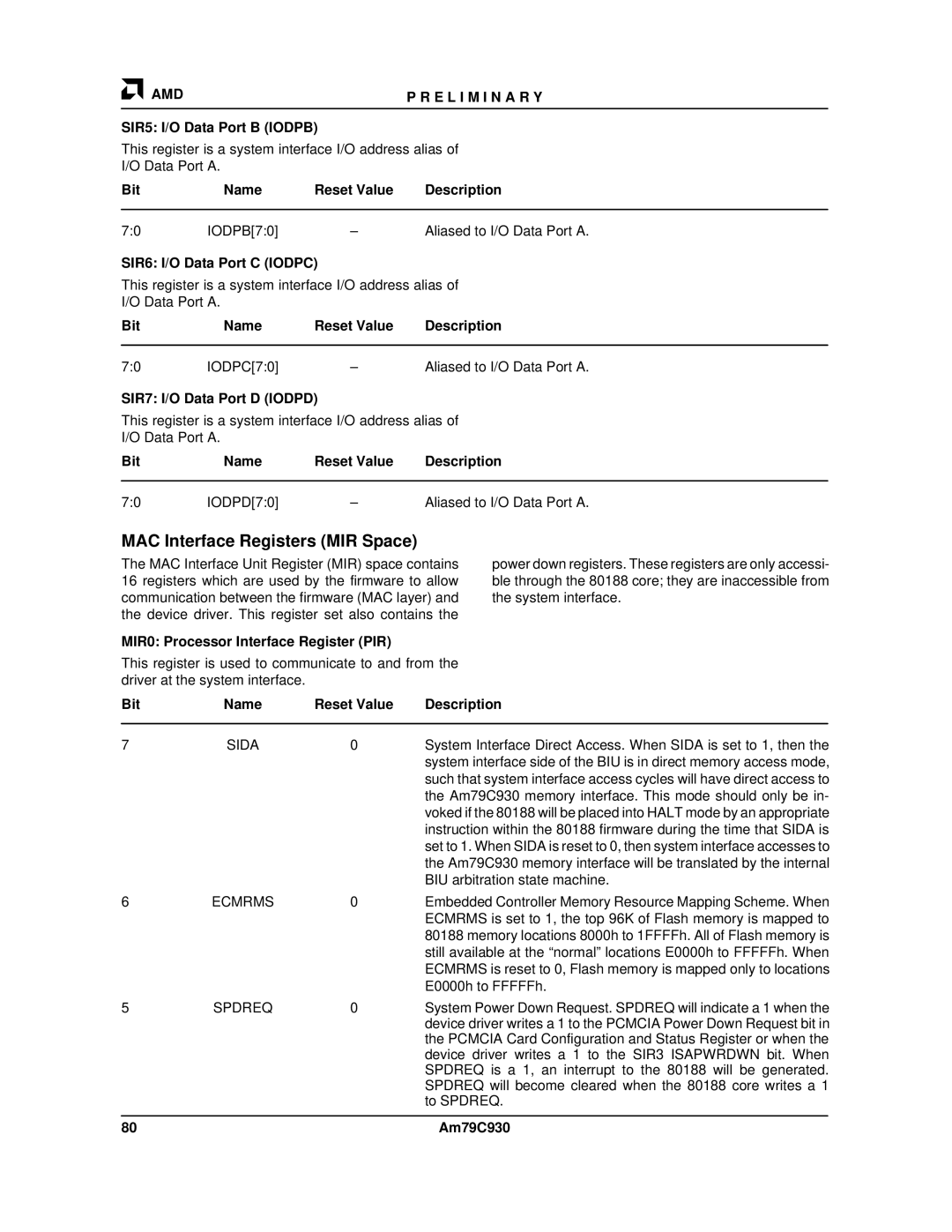

SIR5: I/O Data Port B (IODPB)

This register is a system interface I/O address alias of

I/O Data Port A.

Bit | Name | Reset Value | Description |

|

|

|

|

7:0 | IODPB[7:0] | – | Aliased to I/O Data Port A. |

SIR6: I/O Data Port C (IODPC)

This register is a system interface I/O address alias of

I/O Data Port A.

Bit | Name | Reset Value | Description |

|

|

|

|

7:0 | IODPC[7:0] | – | Aliased to I/O Data Port A. |

SIR7: I/O Data Port D (IODPD)

This register is a system interface I/O address alias of

I/O Data Port A.

Bit | Name | Reset Value | Description |

|

|

|

|

7:0 | IODPD[7:0] | – | Aliased to I/O Data Port A. |

MAC Interface Registers (MIR Space)

The MAC Interface Unit Register (MIR) space contains 16 registers which are used by the firmware to allow communication between the firmware (MAC layer) and the device driver. This register set also contains the

MIR0: Processor Interface Register (PIR)

This register is used to communicate to and from the driver at the system interface.

power down registers. These registers are only accessi- ble through the 80188 core; they are inaccessible from the system interface.

Bit | Name | Reset Value | Description | |

|

|

|

|

|

7 | SIDA | 0 | System Interface Direct Access. When SIDA is set to 1, then the | |

|

|

| system interface side of the BIU is in direct memory access mode, | |

|

|

| such that system interface access cycles will have direct access to | |

|

|

| the Am79C930 memory interface. This mode should only be in- | |

|

|

| voked if the 80188 will be placed into HALT mode by an appropriate | |

|

|

| instruction within the 80188 firmware during the time that SIDA is | |

|

|

| set to 1. When SIDA is reset to 0, then system interface accesses to | |

|

|

| the Am79C930 memory interface will be translated by the internal | |

|

|

| BIU arbitration state machine. | |

6 | ECMRMS | 0 | Embedded Controller Memory Resource Mapping Scheme. When | |

|

|

| ECMRMS is set to 1, the top 96K of Flash memory is mapped to | |

|

|

| 80188 memory locations 8000h to 1FFFFh. All of Flash memory is | |

|

|

| still available at the “normal” locations E0000h to FFFFFh. When | |

|

|

| ECMRMS is reset to 0, Flash memory is mapped only to locations | |

|

|

| E0000h to FFFFFh. | |

5 | SPDREQ | 0 | System Power Down Request. SPDREQ will indicate a 1 when the | |

|

|

| device driver writes a 1 to the PCMCIA Power Down Request bit in | |

|

|

| the PCMCIA Card Configuration and Status Register or when the | |

|

|

| device driver writes a 1 to the SIR3 ISAPWRDWN bit. When | |

|

|

| SPDREQ is a 1, an interrupt to the 80188 will be generated. | |

|

|

| SPDREQ will become cleared when the 80188 core writes a 1 | |

|

|

| to SPDREQ. | |

|

|

|

|

|

80 |

|

| Am79C930 | |