| P R E L I M I N A R Y |

| AMD | |

TXS | 4 X TSCLK |

|

|

|

| TGAP1 X TBCLK |

| TGAP4 X TBCLK | |

| + 2 X TSCLK |

| + 2 X TSCLK | |

T1 |

|

|

|

|

| TGAP2 X TBCLK |

| TGAP3 X TBCLK |

|

T2 | + 2 X TSCLK |

| + 2 X TSCLK |

|

|

|

|

| |

| 2 X TSCLK |

| 2 X TSCLK |

|

T3 |

|

|

|

|

| 3 X TSCLK |

| 7 X TSCLK | |

O_TX |

|

|

|

|

| HDB X TBCLK |

| DRB X TBCLK | |

TXP_ON |

|

|

|

|

TXDATA | TX default bit | 1st | Last | TX default bit |

Data Bit | Data Bit | |||

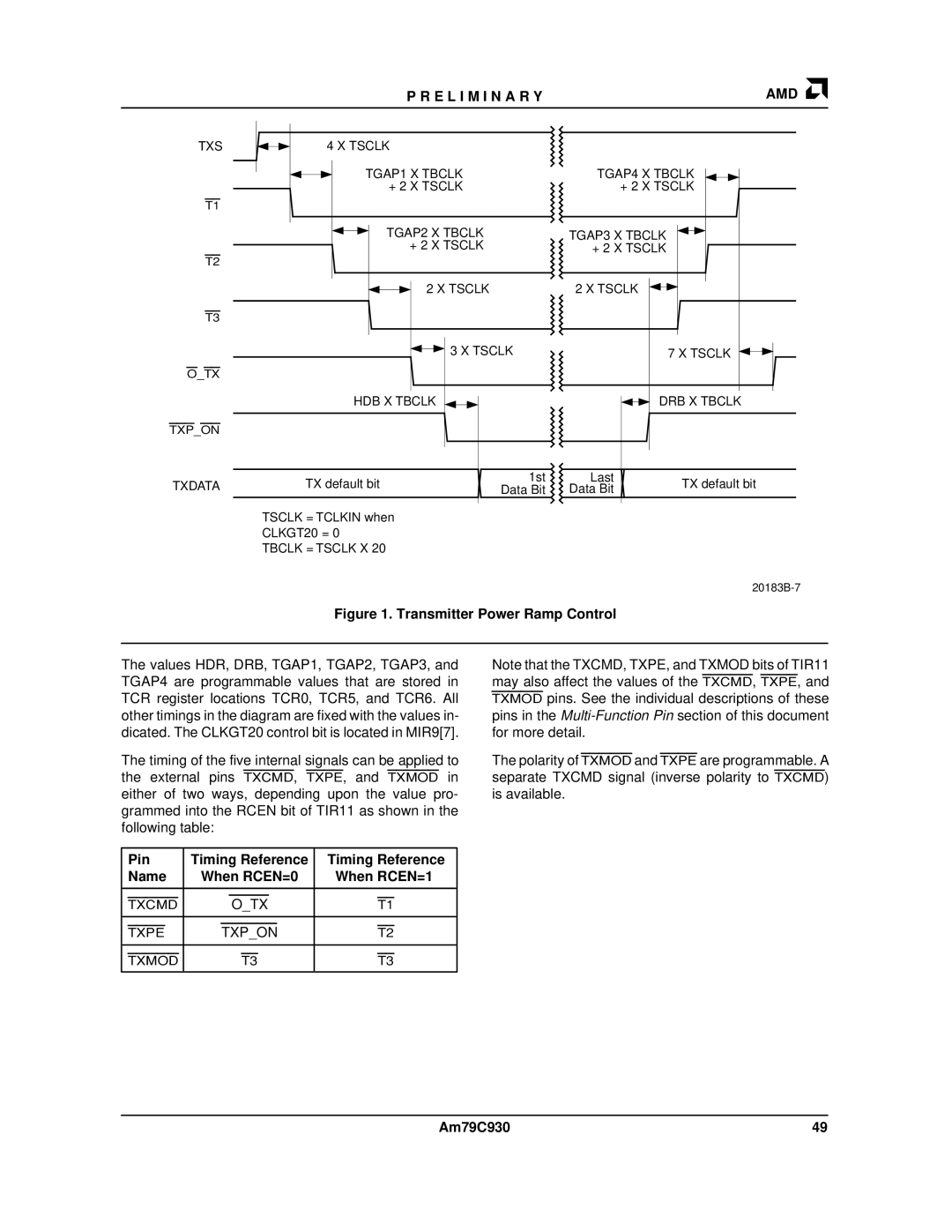

TSCLK = TCLKIN when

CLKGT20 = 0

TBCLK = TSCLK X 20

Figure 1. Transmitter Power Ramp Control

The values HDR, DRB, TGAP1, TGAP2, TGAP3, and TGAP4 are programmable values that are stored in TCR register locations TCR0, TCR5, and TCR6. All other timings in the diagram are fixed with the values in- dicated. The CLKGT20 control bit is located in MIR9[7].

The timing of the five internal signals can be applied to the external pins TXCMD, TXPE, and TXMOD in either of two ways, depending upon the value pro- grammed into the RCEN bit of TIR11 as shown in the following table:

Pin | Timing Reference | Timing Reference | ||||

Name | When RCEN=0 | When RCEN=1 | ||||

|

|

|

|

|

|

|

TXCMD |

|

|

|

|

| T1 |

|

| O_TX | ||||

|

|

|

|

|

|

|

TXPE |

|

| T2 | |||

| TXP_ON |

| ||||

|

|

|

|

|

|

|

TXMOD |

|

| T3 | T3 | ||

|

|

|

|

|

|

|

Note that the TXCMD, TXPE, and TXMOD bits of TIR11 may also affect the values of the TXCMD, TXPE, and TXMOD pins. See the individual descriptions of these pins in the

The polarity of TXMOD and TXPE are programmable. A separate TXCMD signal (inverse polarity to TXCMD) is available.

Am79C930 | 49 |