AMD | P R E L I M I N A R Y |

|

|

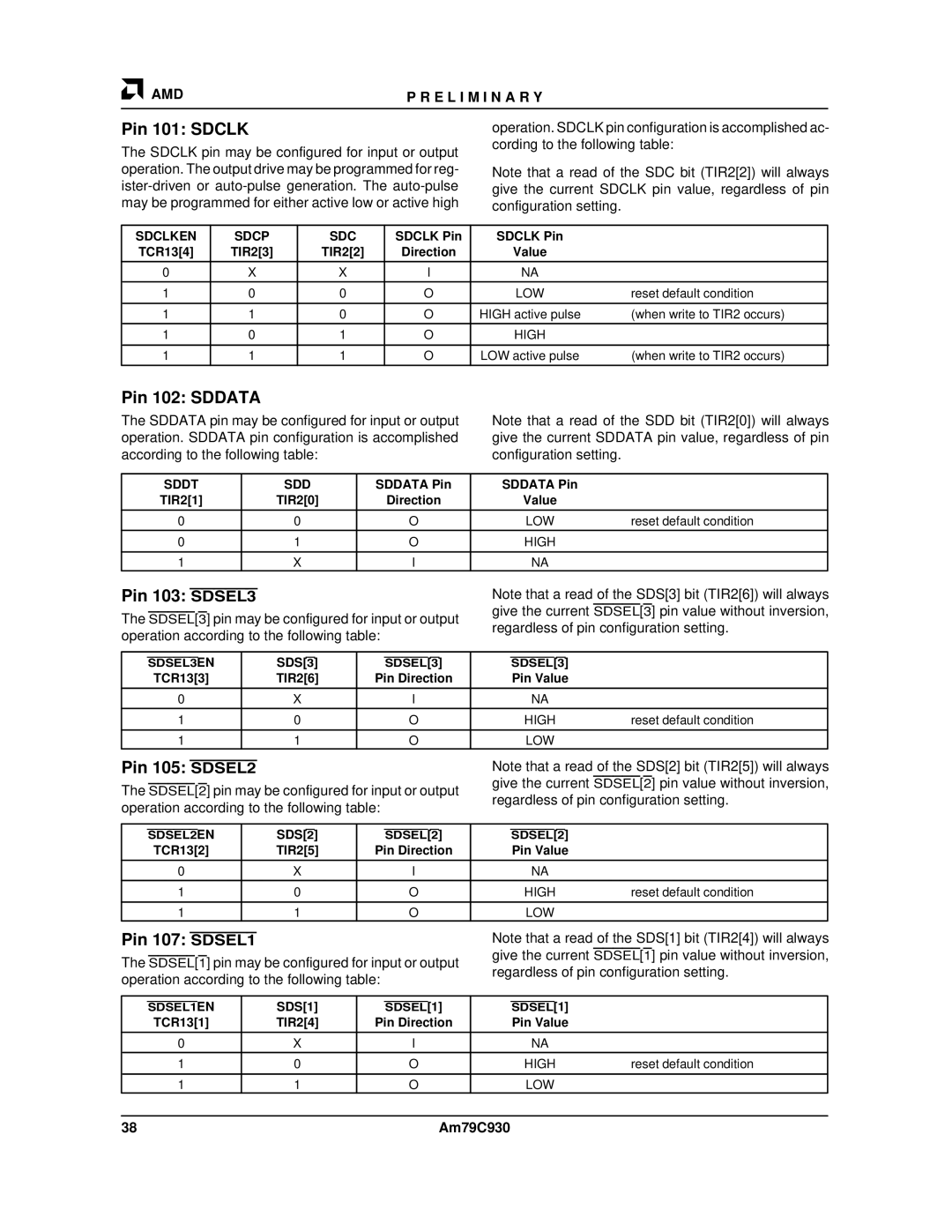

Pin 101: SDCLK

The SDCLK pin may be configured for input or output operation. The output drive may be programmed for reg-

operation. SDCLK pin configuration is accomplished ac- cording to the following table:

Note that a read of the SDC bit (TIR2[2]) will always give the current SDCLK pin value, regardless of pin configuration setting.

SDCLKEN | SDCP | SDC | SDCLK Pin | SDCLK Pin |

|

TCR13[4] | TIR2[3] | TIR2[2] | Direction | Value |

|

|

|

|

|

|

|

0 | X | X | I | NA |

|

1 | 0 | 0 | O | LOW | reset default condition |

|

|

|

|

|

|

1 | 1 | 0 | O | HIGH active pulse | (when write to TIR2 occurs) |

|

|

|

|

|

|

1 | 0 | 1 | O | HIGH |

|

|

|

|

|

|

|

1 | 1 | 1 | O | LOW active pulse | (when write to TIR2 occurs) |

|

|

|

|

|

|

Pin 102: SDDATA

The SDDATA pin may be configured for input or output operation. SDDATA pin configuration is accomplished according to the following table:

Note that a read of the SDD bit (TIR2[0]) will always give the current SDDATA pin value, regardless of pin configuration setting.

SDDT | SDD | SDDATA Pin | SDDATA Pin |

|

TIR2[1] | TIR2[0] | Direction | Value |

|

|

|

|

|

|

0 | 0 | O | LOW | reset default condition |

0 | 1 | O | HIGH |

|

|

|

|

|

|

1 | X | I | NA |

|

Pin 103: SDSEL3

The SDSEL[3] pin may be configured for input or output operation according to the following table:

Note that a read of the SDS[3] bit (TIR2[6]) will always give the current SDSEL[3] pin value without inversion, regardless of pin configuration setting.

SDSEL3EN | SDS[3] | SDSEL[3] | SDSEL[3] |

|

TCR13[3] | TIR2[6] | Pin Direction | Pin Value |

|

0 | X | I | NA |

|

|

|

|

|

|

1 | 0 | O | HIGH | reset default condition |

|

|

|

|

|

1 | 1 | O | LOW |

|

Pin 105: SDSEL2

The SDSEL[2] pin may be configured for input or output operation according to the following table:

Note that a read of the SDS[2] bit (TIR2[5]) will always give the current SDSEL[2] pin value without inversion, regardless of pin configuration setting.

SDSEL2EN | SDS[2] | SDSEL[2] | SDSEL[2] |

|

TCR13[2] | TIR2[5] | Pin Direction | Pin Value |

|

|

|

|

|

|

0 | X | I | NA |

|

1 | 0 | O | HIGH | reset default condition |

|

|

|

|

|

1 | 1 | O | LOW |

|

Pin 107: SDSEL1

The SDSEL[1] pin may be configured for input or output operation according to the following table:

Note that a read of the SDS[1] bit (TIR2[4]) will always give the current SDSEL[1] pin value without inversion, regardless of pin configuration setting.

SDSEL1EN | SDS[1] | SDSEL[1] |

| SDSEL[1] |

|

TCR13[1] | TIR2[4] | Pin Direction |

| Pin Value |

|

|

|

|

|

|

|

0 | X | I |

| NA |

|

|

|

|

|

|

|

1 | 0 | O |

| HIGH | reset default condition |

|

|

|

|

|

|

1 | 1 | O |

| LOW |

|

|

|

|

|

|

|

38 |

| Am79C930 |

|

| |