| AMD |

| P R E L I M I N A R Y | |

|

|

|

|

|

|

|

| In addition to these bits, the USER6/IRQ5 pin may be used to pro- | |

|

|

| duce interrupts to the 80188 embedded controller. This capability is | |

|

|

| controlled by the ENXSDF bit of TCR28 and the SDFU bit of TIR5 | |

|

|

| and operates independently of the bits in the table above. | |

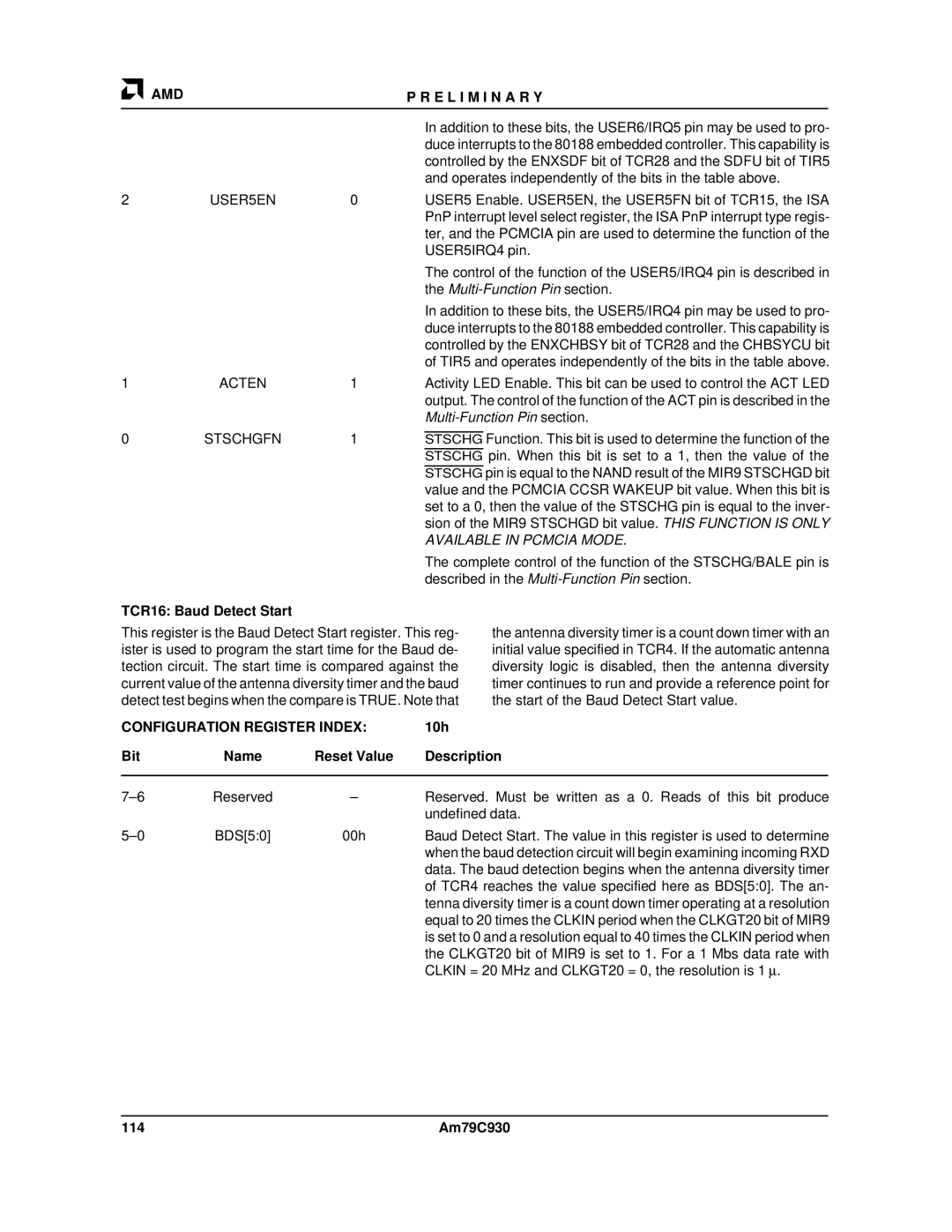

2 | USER5EN | 0 | USER5 Enable. USER5EN, the USER5FN bit of TCR15, the ISA | |

|

|

| PnP interrupt level select register, the ISA PnP interrupt type regis- | |

|

|

| ter, and the PCMCIA pin are used to determine the function of the | |

|

|

| USER5IRQ4 pin. | |

|

|

| The control of the function of the USER5/IRQ4 pin is described in | |

|

|

| the | |

|

|

| In addition to these bits, the USER5/IRQ4 pin may be used to pro- | |

|

|

| duce interrupts to the 80188 embedded controller. This capability is | |

|

|

| controlled by the ENXCHBSY bit of TCR28 and the CHBSYCU bit | |

|

|

| of TIR5 and operates independently of the bits in the table above. | |

1 | ACTEN | 1 | Activity LED Enable. This bit can be used to control the ACT LED | |

|

|

| output. The control of the function of the ACT pin is described in the | |

|

|

|

| |

0 | STSCHGFN | 1 | STSCHG Function. This bit is used to determine the function of the | |

|

|

| STSCHG pin. When this bit is set to a 1, then the value of the | |

|

|

| STSCHG pin is equal to the NAND result of the MIR9 STSCHGD bit | |

|

|

| value and the PCMCIA CCSR WAKEUP bit value. When this bit is | |

set to a 0, then the value of the STSCHG pin is equal to the inver- sion of the MIR9 STSCHGD bit value. THIS FUNCTION IS ONLY AVAILABLE IN PCMCIA MODE.

The complete control of the function of the STSCHG/BALE pin is described in the

TCR16: Baud Detect Start

This register is the Baud Detect Start register. This reg- ister is used to program the start time for the Baud de- tection circuit. The start time is compared against the current value of the antenna diversity timer and the baud detect test begins when the compare is TRUE. Note that

the antenna diversity timer is a count down timer with an initial value specified in TCR4. If the automatic antenna diversity logic is disabled, then the antenna diversity timer continues to run and provide a reference point for the start of the Baud Detect Start value.

CONFIGURATION REGISTER INDEX: | 10h | ||

Bit | Name | Reset Value | Description |

|

|

|

|

Reserved | – | Reserved. Must be written as a 0. Reads of this bit produce | |

|

|

| undefined data. |

BDS[5:0] | 00h | Baud Detect Start. The value in this register is used to determine | |

when the baud detection circuit will begin examining incoming RXD data. The baud detection begins when the antenna diversity timer of TCR4 reaches the value specified here as BDS[5:0]. The an- tenna diversity timer is a count down timer operating at a resolution equal to 20 times the CLKIN period when the CLKGT20 bit of MIR9 is set to 0 and a resolution equal to 40 times the CLKIN period when the CLKGT20 bit of MIR9 is set to 1. For a 1 Mbs data rate with CLKIN = 20 MHz and CLKGT20 = 0, the resolution is 1 μ.

114 | Am79C930 |