AMD | P R E L I M I N A R Y |

|

|

has also been set to a 1 and the PCMCIA pin is set to 1. The value that is read from this bit represents the current value of the TXDATA pin of the Am79C930 device.

A complete description of the control of the function of the TXDATA pin is described in the

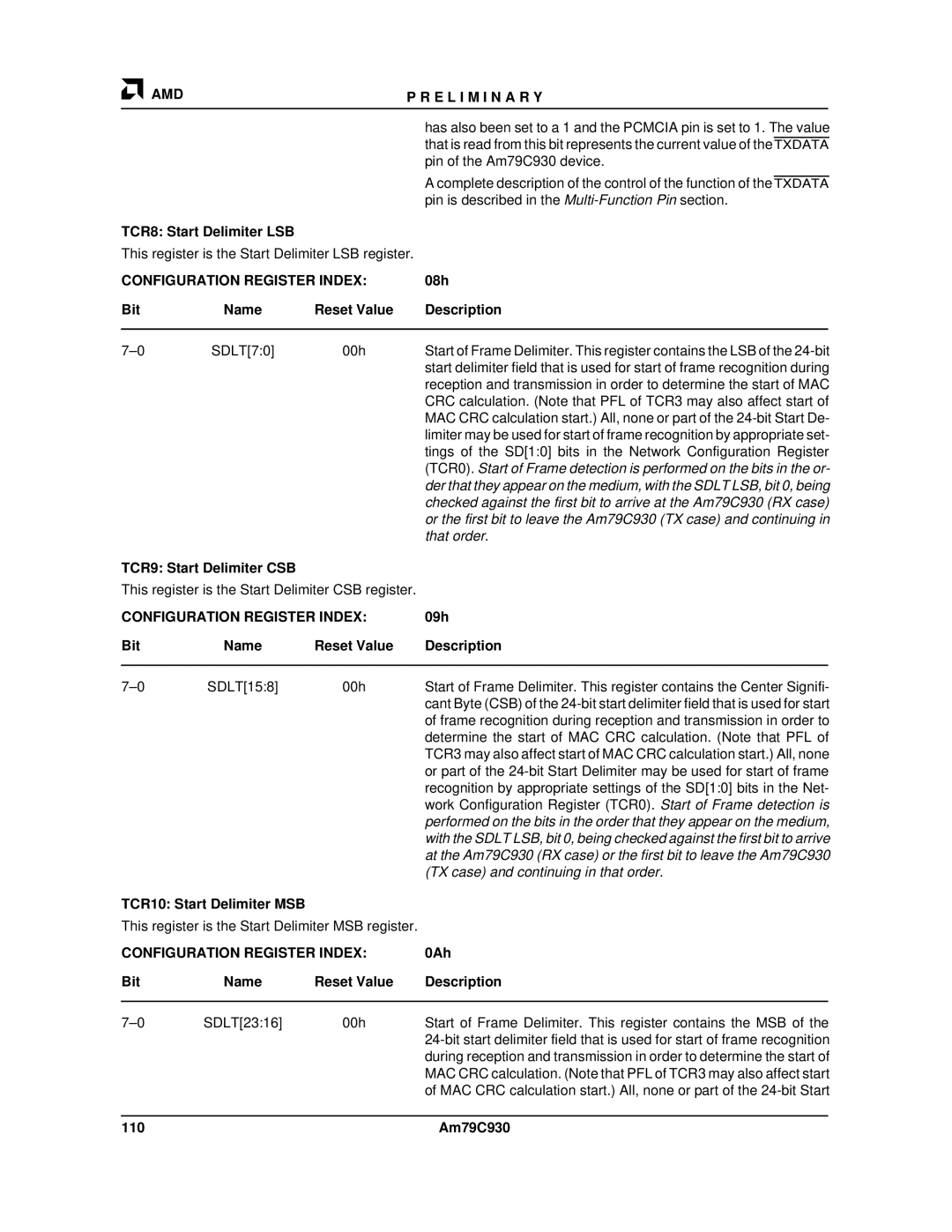

TCR8: Start Delimiter LSB

This register is the Start Delimiter LSB register.

CONFIGURATION REGISTER INDEX: | 08h | ||

Bit | Name | Reset Value | Description |

|

|

|

|

SDLT[7:0] | 00h | Start of Frame Delimiter. This register contains the LSB of the | |

start delimiter field that is used for start of frame recognition during reception and transmission in order to determine the start of MAC CRC calculation. (Note that PFL of TCR3 may also affect start of MAC CRC calculation start.) All, none or part of the

TCR9: Start Delimiter CSB

This register is the Start Delimiter CSB register.

CONFIGURATION REGISTER INDEX: | 09h | ||

Bit | Name | Reset Value | Description |

|

|

|

|

SDLT[15:8] | 00h | Start of Frame Delimiter. This register contains the Center Signifi- | |

cant Byte (CSB) of the

TCR10: Start Delimiter MSB

This register is the Start Delimiter MSB register.

CONFIGURATION REGISTER INDEX: | 0Ah | |||

Bit | Name | Reset Value | Description | |

|

|

|

|

|

SDLT[23:16] | 00h | Start of Frame Delimiter. This register contains the MSB of the | ||

|

|

| ||

|

|

| during reception and transmission in order to determine the start of | |

|

|

| MAC CRC calculation. (Note that PFL of TCR3 may also affect start | |

|

|

| of MAC CRC calculation start.) All, none or part of the | |

|

|

|

|

|

110 |

|

| Am79C930 | |