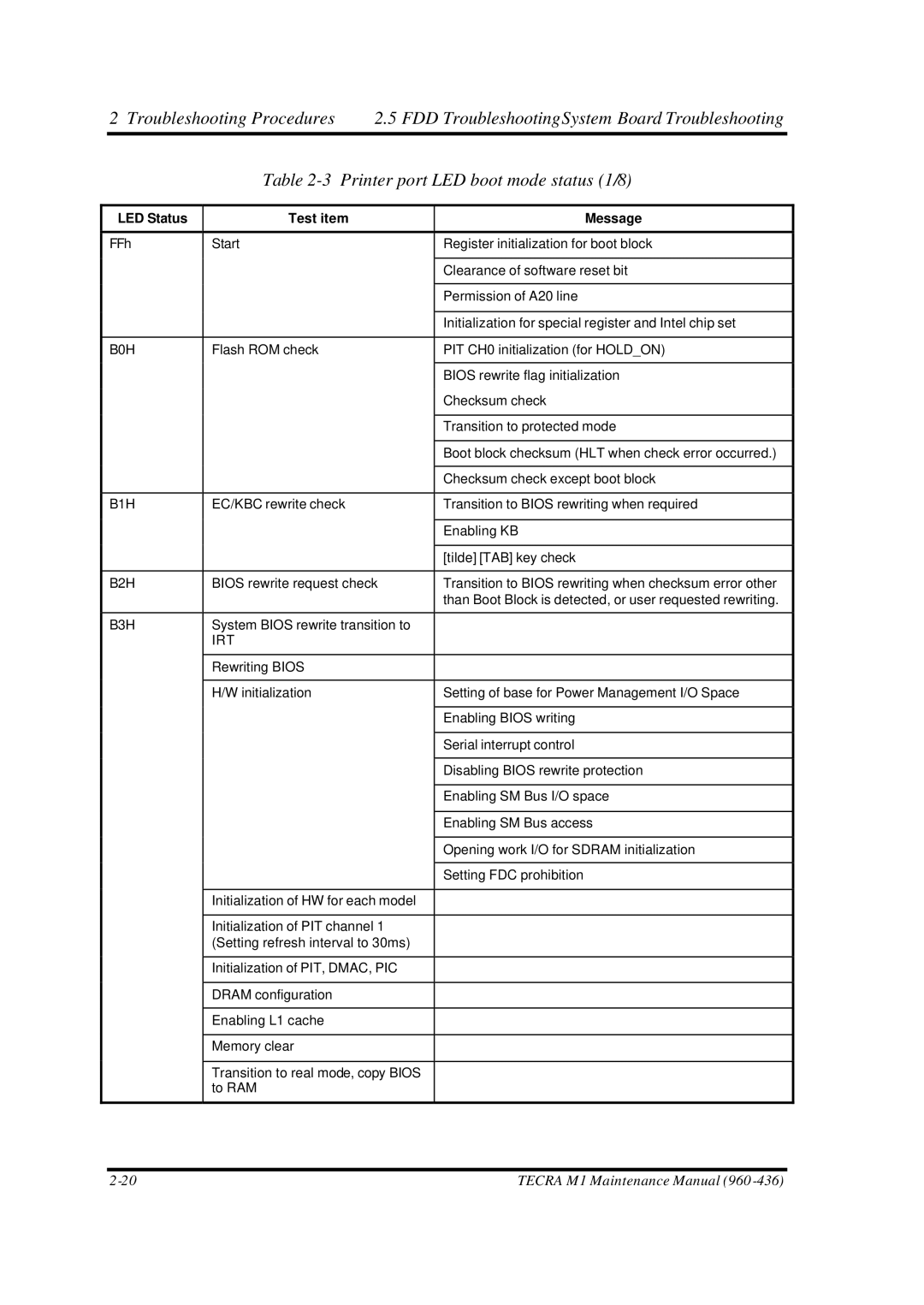

2 Troubleshooting Procedures | 2.5 FDD TroubleshootingSystem Board Troubleshooting |

Table 2-3 Printer port LED boot mode status (1/8)

LED Status | Test item | Message |

|

|

|

FFh | Start | Register initialization for boot block |

|

|

|

|

| Clearance of software reset bit |

|

|

|

|

| Permission of A20 line |

|

|

|

|

| Initialization for special register and Intel chip set |

|

|

|

B0H | Flash ROM check | PIT CH0 initialization (for HOLD_ON) |

|

|

|

|

| BIOS rewrite flag initialization |

|

| Checksum check |

|

|

|

|

| Transition to protected mode |

|

|

|

|

| Boot block checksum (HLT when check error occurred.) |

|

|

|

|

| Checksum check except boot block |

|

|

|

B1H | EC/KBC rewrite check | Transition to BIOS rewriting when required |

|

|

|

|

| Enabling KB |

|

|

|

|

| [tilde] [TAB] key check |

|

|

|

B2H | BIOS rewrite request check | Transition to BIOS rewriting when checksum error other |

|

| than Boot Block is detected, or user requested rewriting. |

|

|

|

B3H | System BIOS rewrite transition to |

|

| IRT |

|

|

|

|

| Rewriting BIOS |

|

|

|

|

| H/W initialization | Setting of base for Power Management I/O Space |

|

|

|

|

| Enabling BIOS writing |

|

|

|

|

| Serial interrupt control |

|

|

|

|

| Disabling BIOS rewrite protection |

|

|

|

|

| Enabling SM Bus I/O space |

|

|

|

|

| Enabling SM Bus access |

|

|

|

|

| Opening work I/O for SDRAM initialization |

|

|

|

|

| Setting FDC prohibition |

|

|

|

| Initialization of HW for each model |

|

|

|

|

| Initialization of PIT channel 1 |

|

| (Setting refresh interval to 30ms) |

|

|

|

|

| Initialization of PIT, DMAC, PIC |

|

|

|

|

| DRAM configuration |

|

|

|

|

| Enabling L1 cache |

|

|

|

|

| Memory clear |

|

|

|

|

| Transition to real mode, copy BIOS |

|

| to RAM |

|

|

|

|

TECRA M1 Maintenance Manual (960 |