FrameSaver SLV

Trademarks

Warranty, Sales, Service, and Training Information

Copyright 2002 Paradyne Corporation All rights reserved

Document Feedback

Contents

September

ConfigurationTProcedures

Configuration Options

Iii

Configuring the FrameSaver SLV Router

Operation and Maintenance

Security and Logins

Troubleshooting

Lamp Test

Vii

Setting Up NetScout Manager Plus for FrameSaver Devices

Setting Up Network Health for FrameSaver Devices

Menu HierarchyT

Viii

Snmp MIBs and Traps, and Rmon Alarm Defaults

Router CLI TCommands, Codes, and Designations

Connectors, Cables, and Pin Assignments

Router Command Line Summaries and Shortcuts

Index

Technical Specifications Equipment List

Section Description

Purpose and Intended Audience

Document Organization

Section Description

Xii

Document Number Document Title

Product-Related Documents

Xiii

Xiv

Conventions Used

System Overview

About the FrameSaver SLV

Router-Specific Features

CSU/DSU-Specific Features

About the FrameSaver SLV

FrameSaver Diagnostic and SLM Feature Sets

FrameSaver Diagnostic Feature Set

Through 120 Connections PVCs Dedicated Management

FrameSaver SLV Feature Router

Maximum Number of PVCs and Management PVCs Supported

About the FrameSaver SLV

About the FrameSaver SLV

Additional FrameSaver SLV 9128-II Features

Additional FrameSaverTSLV 9126-II and 9128-II Features

FrameSaver SLM Feature Set

OpenLane SLM System

NetScout Manager Plus and NetScout Probes

User Interface and Basic Operation

Logging On

Procedure

If your login was Hen

Select

Main Menu

Screen Format Description

Screen Work Areas

Press

Navigating the Screens

Keyboard Keys

For the screen Select Function Press Enter to

Function Keys

Selecting from a Menu

Switching Between Screen Areas

Entering Information

Screen Contents

Selecting a Field

CLI Keyboard Keys

Navigating the Router’s CLI

Basic Configuration

Configuration Procedures

Isdn

Configuration Menu

Configuration Option Area Description

Configuration Option Areas

Main Menu → Configuration

Accessing and Displaying Configuration Options

Configuration → PVC Connections

Changing Configuration Options

Saving Configuration Options

Configuration Options

Configuration Options

Easy Install Screen Example

Using the Easy Install Feature

Main Menu → Easy Install

Configuration → Data Ports→ Dlci Records

Using RIP with FrameSaver SLV CSU/DSUs

If the selection is Enter

Entering System Information and Setting the System Clock

Main Menu → Control→ System Information

Valid characters include For

Setting Up the Modem

Setting Up Call Directories for Trap Dial-Out

Main Menu → Control→ Modem Call Directories

Setting Up to Use the Modem PassThru Feature

Auto-Configuration Screen Example

Setting Up Auto-Configuration

Main Menu → Auto-Configuration

Only applies to models with

Selecting a Frame Relay Discovery Mode

Main Menu → Auto-Configuration→Frame Relay Discovery Mode

Discovery Mode Configuration Description

Discovery Mode Configuration Description

Automatically Removing a Circuit

Main Menu → Configuration → Isdn → Physical

Setting Up Dial Backup

Setting Up the DBM Physical Interface

If you select Then

Setting Up Automatic Backup Configuration

Following prompt When Appears If you select

Delete unused

Remove Alternate

Destinations

From PVCs

Modifying Isdn Link Profiles

Main Menu → Configuration → Isdn → Link Profiles

For Originating a Backup Call For Answering a Backup Call

Main Menu → Configuration → Auto-Backup Criteria

Restricting Automatic Backup and Configuring Backup Timers

Assigning DLCIs to a Backup Group

Configuring the DBM Interface to Send Snmp Traps

Main Menu → Control→ Change Operating Mode

PVC Backup Over the Network Interface

Setting Up Back-to-Back Operation

Changing Operating Mode

Configuration Option Tables

System Frame Relay and LMI Options 1

Configuring the Overall System

Configuring Frame Relay and LMI for the System CSU/DSUs

Main Menu → Configuration → System → Frame Relay and LMI

System Frame Relay and LMI Options 2

System Frame Relay and LMI Options 3

LMI Status Enquiry N1 Possible Settings 1, 2, 3, 4

LMI Heartbeat T1 Possible Settings 5, 10, 15, 20, 25

System Frame Relay and LMI Options 4

Field Setting After RfcCodePoints Selected

Configuring Class of Service Definitions

Code Points Assigned

Class of Service Definitions

Class of Svc Name

Measure Latency & Availability

Name

Code Point Definitions

Code Point Definitions

Code Pnt

SLV Sample Interval secs

Configuring Service Level Verification Options

Service Level Verification Options 1

SLV Type Available Settings Standard, COS 1-COS

SLV Timeout Clearing Event Threshold

Service Level Verification Options 2

Dlci Down on SLV Timeout

SLV Timeout Error Event Threshold

SLV Packet Size bytes

Service Level Verification Options 3

SLV Latency Clearing Event Threshold

General System Options 1

Configuring General System Options

Main Menu → Configuration → System→ General

Test Timeout

General System Options 2

General System Options 3

System Alarm Relay

Network Physical Interface Options 1

Configuring Physical Interfaces

Configuring the Network Interface

Main Menu → Configuration → Network→ Physical

Transmit Timing

Line Build Out LBO Possible Settings 0.0, -7.5, -15

Network Physical Interface Options 2

Bit Stuffing

Ansi Performance Report Messages

Network Initiated Dclb Possible Settings Disable, V.54&ANSI

Network Physical Interface Options 3

Network Initiated PLB

Circuit Identifier

Network Physical Interface Options 4

Data Port Physical Interface Options 1

Configuring a User Data Port CSU/DSUs

Main Menu → Configuration → Data Ports→ Physical

Port Use Possible Settings Frame Relay, Synchronous Data

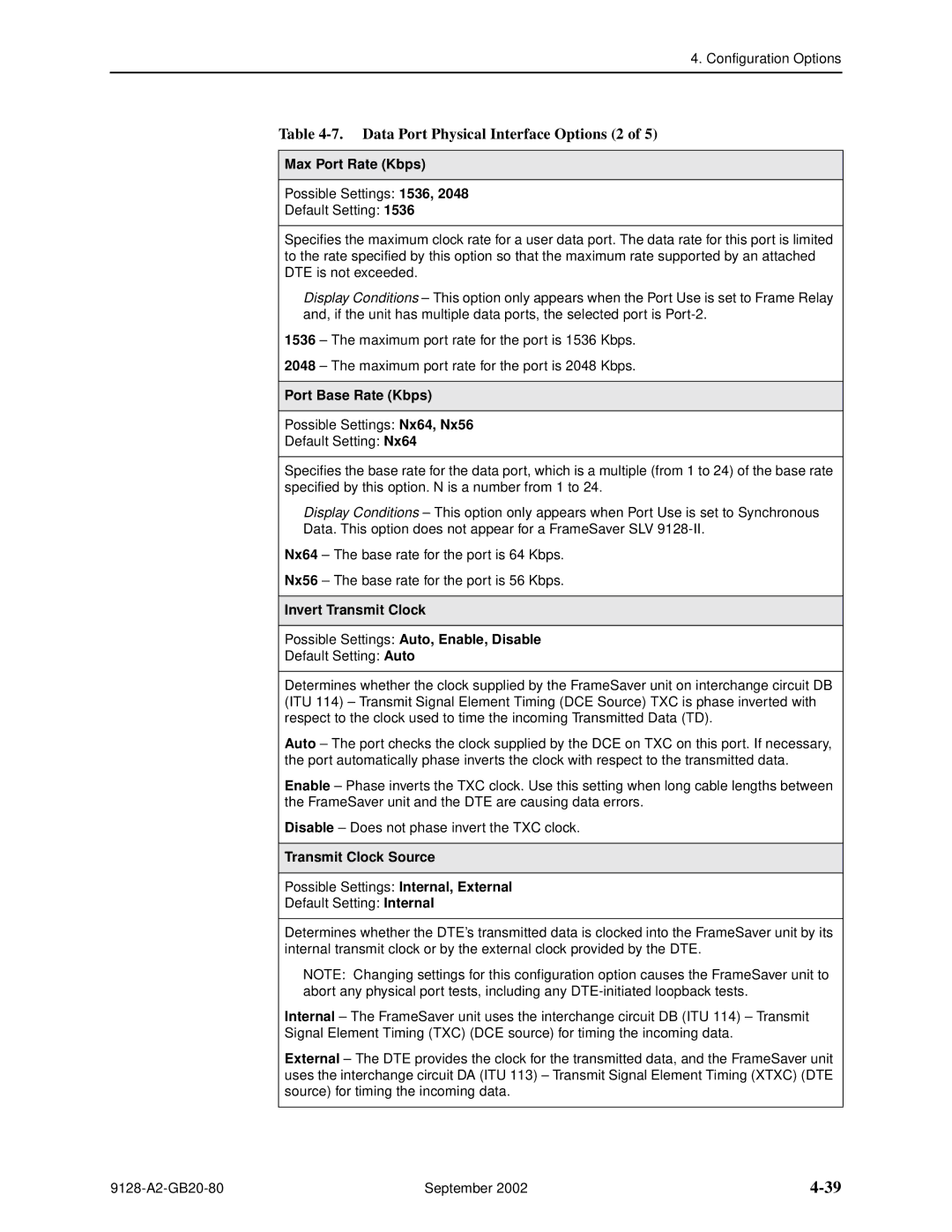

Transmit Clock Source

Data Port Physical Interface Options 2

Max Port Rate Kbps

Port Base Rate Kbps

Monitor DTR

Data Port Physical Interface Options 3

Monitor RTS Control

Invert Transmit and Receive Data

Data Port Physical Interface Options 4

Port DTE Initiated Loopbacks

Data Port Physical Interface Options 5

Action on Network Yellow Alarm

Interface Status

Configuring the DSX-1 Interface

Main Menu → Configuration → DSX-1

DSX-1 Physical Interface Options 1

Send All Ones on DSX-1 Failure

DSX-1 Physical Interface Options 2

Local Phone Number 1 or

Configuring the Isdn DBM Interface

Service Profile ID Spid 1 or

Isdn BRI DBM Physical Interface Options

Local Phone Number

Switch Type Possible Settings NI-2, ATT4ESS, ATT5ESS

10. Isdn PRI DBM Physical Interface Options 1

10. Isdn PRI DBM Physical Interface Options 2

10. Isdn PRI DBM Physical Interface Options 3

Link Name

Setting Up Isdn Link Profiles

Main Menu → Configuration → Isdn → Isdn Link Profiles

11. Isdn Link Profile Options 1

Maximum Link Rate Kbps

11. Isdn Link Profile Options 2

Outbound Phone Number

Inbound Calling ID 1 or

Alternate Outbound Phone Number

Assigning Time Slots/Cross Connections

11. Isdn Link Profile Options 3

Caller Identification Method

Value Meaning

Assigning Frame Relay Time Slots to the Network Interface

Frame Relay Network Time Slot Assignment Screen Example

Ntt

Assigning DSX-1 Time Slots to the Network Interface

Time Slot Assignment Rule

Ime Slot Assignment Rules

DSX-1 to Network Time Slot Assignment Screen Example

DSX-1 Signaling Assignments and Trunk Conditioning

RBS

Idle

PLAR3idle

Sync Data Port Assignment

Synchronous Data Port Assignment Screen Example

Physical Interface Options

Clearing Assignments

LMI

Configuring Frame Relay for an Interface

13. Interface Frame Relay Options 1

Frame Relay DS0s Base Rate

13. Interface Frame Relay Options 2

Traffic Policing

LMI Parameters

13. Interface Frame Relay Options 3

Dlci Number

Manually Configuring Dlci Records

14. Dlci Record Options 1

Committed Burst Size Bc Bits

14. Dlci Record Options 2

CIR bps

Outbound Management Priority

14. Dlci Record Options 3

Excess Burst Size Bits

Dlci Priority

14. Dlci Record Options 4

Backup Group Possible Settings A, B, C, . . . Z, None

Source Dlci

Configuring PVC Connections

Main Menu → Configuration → PVC Connections

15. PVC Connection Options 1

Primary Destination Dlci

15. PVC Connection Options 2

Source Edlci

Primary Destination Link

Alternate Destination Dlci

15. PVC Connection Options 3

Primary Destination Edlci

Alternate Destination Link

Alternate Destination Edlci

15. PVC Connection Options 4

Enter IP Address press ESC to abort ... FWD No

Configuring the IP Path List

Main Menu → Configuration → IP Path List Static

16. IP Path List

Setting Up Management and Communication Options

17. Node IP Options 1

Configuring Node IP Information

17. Node IP Options 2

TS Access Management Link

TS Management Snmp Validation

17. Node IP Options 3

18. Management PVC Options 1

Configuring Management PVCs

Set DE

18. Management PVC Options 2

Payload Managed

Primary Dlci

18. Management PVC Options 3

Primary Edlci

18. Management PVC Options 4

Alternate Edlci

18. Management PVC Options 5

Alternate Dlci

Encapsulation

18. Management PVC Options 6

Snmp Management

Configuring General Snmp Management

Name 1 Access

19. General Snmp Management Options 1

19. General Snmp Management Options 2

Configuring Telnet and/or FTP Session Support

Name 2 Access

Telnet Session

Telnet Login Required

20. Telnet and FTP Session Options 1

20. Telnet and FTP Session Options 2

Number of Managers

Configuring Snmp NMS Security

21. Snmp NMS Security Options 1

NMS IP Validation

22. Snmp Traps and Trap Dial-Out Options 1

Configuring Snmp Traps and Trap Dial-Out

21. Snmp NMS Security Options 2

22. Snmp Traps and Trap Dial-Out Options 2

Enterprise Specific Traps

Link Traps Possible Settings Disable, Up, Down, Both

22. Snmp Traps and Trap Dial-Out Options 3

Rmon Traps

Possible Settings Network, Ports, DBM, All, None

22. Snmp Traps and Trap Dial-Out Options 4

Dlci Traps on Interfaces Filter Selection Field

Trap Disconnect

Dial-Out Delay TIme Min

22. Snmp Traps and Trap Dial-Out Options 5

Trap Dial-Out

IP SLV Availability Traps

22. Snmp Traps and Trap Dial-Out Options 6

Alternate Dial-Out Directory

Latency Traps

23. Ethernet Management Options 1

Configuring Ethernet Management

Proxy ARP

23. Ethernet Management Options 2

Character Length

Configuring the Communication Port

24. Communication Port Options 1

Stop Bits

Login Required

24. Communication Port Options 2

Parity

24. Communication Port Options 3

RIP

24. Communication Port Options 4

25. Modem Port Options 1

Configuring the Modem Port

100

24. Communication Port Options 5

25. Modem Port Options 2

101

25. Modem Port Options 3

102

25. Modem Port Options 4

103

104

Configuring the Criteria for Automatic Backup

Main Menu → Configuration → Auto Backup Criteria

26. Auto Backup Criteria Options 1

Backup Allowed Day To nnnn

26. Auto Backup Criteria Options 2

When Auto Backup Allowed

Backup Allowed Day From nnnn

106

Configuring the FrameSaver SLV Router

Ethernet

FrameSaver SLV Router Overview

Network Interface

Proxy ARP

Address Resolution Protocol

IP Routing

Interface Configuration

Applications Supported by NAT

Network Address Translation

IP Options Processing

NAT Mapping Public IP Addresses Private IP Addresses

NAT Configuration Example

Save exit

Napt Mapping Public IP Address Private IP Addresses

Napt Configuration Example

Network Address Port Translation

Int ethernet 0 ip nat inside int serial 0.x ip nat outside

Access-list 1 permit 10.1.3.0

Ip nat inside source list 1 interface se 0.x overload

Ip nat inside source static 10.1.1.1

NAT and Napt Configuration Example

Dynamic Host Configuration Protocol Server

Public IP Addresses for NAT Private IP Addresses

Dhcp Server with NAT Configuration Example

Dhcp Relay Agent

Dhcp Server at Remote Site Configuration Example

Bridge Filtering

Router Security

IP Router Filtering

Smurf Attack Prevention

Provisioning the Router Interface

IP Filtering

Land Bug Prevention

Configuring the Router Using Terminal Emulation

Security and Logins

Controlling Asynchronous Terminal Access

Limiting Access

Set the configuration option

Limiting Dial-In Access via the Modem Port

Isdn Call Security

Controlling Isdn Access

Disabling Isdn Access

Limiting Telnet Access

Controlling Telnet or FTP Access

Limiting FTP Access

Has a Level-1 login and Level-2 telnet access has

Disabling Snmp Access

Controlling Snmp Access

Assigning Snmp Community Names and Access Levels

Management and Communication →

Limiting Snmp Access Through IP Addresses

Main Menu → Configuration →

General Snmp Management → Snmp Management Enable

Field Enter

Creating a Login

Main Menu → Control→ Administer Logins

Deleting a Login

Modifying a Login

Largo

Controlling Router CLI Access

Access Levels Command Modes

End

Changing Access Levels

Enable

Enable password password

Security and Logins September

Operation and Maintenance

Operation and Maintenance

View this field To find

Displaying System Information

Main Menu → Status → Identity

Isdn DBM

Viewing LEDs and Control Leads

FrameSaver SLV 9126 LEDs and Control Leads

FrameSaverTM SLV

Display LEDs & Control Leads Screen for a FrameSaver SLV

Main Menu → Status → Display LEDs and Control Leads

Main Menu → Status → Display LEDs and Control Leads

FrameSaver SLV 9128-II LEDs and Control Leads

ALM

LED Descriptions

General Status LEDs 1

Label Indiction Color What It Means

9128-II

General Status LEDs 2

Contd

Model

Ethernet Port LED Routers Only

Network, DSX, or PRI Interface LEDs

Label Indication Color What It Means

User Data Port LED CSU/DSUs Only

User Data Port

Control Lead Descriptions

Additional Control Leads Label Indication What It Means

Network Interface

Terminal

Device Messages

Device Messages 1 What It Indicates What To Do

Seen at an FTP

See Changing Software on

Device Messages 2 What It Indicates What To Do

PVC

Device Messages 3 What It Indicates What To Do

Device Messages 4 What It Indicates What To Do

II only

Reset COM Port usage

Device Messages 5 What It Indicates What To Do

FrameSaver SLV

Device Messages 6 What It Indicates What To Do

Status Menu Example

Status Information

Self-Test Results Messages

Last System Reset Date and Time

System and Test Status Messages

Main Menu → Status → System and Test Status

Isdn PRI DBM only

Change Operating Mode

Health and Status Messages

Health and Status Messages 1 What It Indicates

FrameSaver SLV 9126-II or

Health and Status Messages 2 What It Indicates

Frame relay link 1,2

Health and Status Messages 3 What It Indicates

Framerelaylink 1,2

Health and Status Messages 4 What It Indicates

Nnnn, framerelaylink 1,2

Series Access Carrier only

Health and Status Messages 5 What It Indicates

PathIP Address Down

Health and Status Messages 6 What It Indicates

Relay Network Assignments and an LMI failure is

Configuration→ Time Slot Assignment → Frame

Health and Status Messages 7 What It Indicates

Framerelaylink 1 ,3

Test Status Messages

Test Status Messages 1 What It Indicates

Dclb Active, framerelaylink 1 or

Test Status Messages 2 What It Indicates

LMI-Reported DLCIs Status Screen Example

Network LMI-Reported DLCIs Status

Main Menu → Status→ LMI Reported DLCIs

Tframe relay network, or

IP Path Connection Status Screen Example

IP Path Connection Status

Main Menu → Status→ IP Path Connection Status

11. IP Path Connection Status Field What It Indicates

PVC Connection Status Screen Example

PVC Connection Status

Main Menu → Status→ PVC Connection Status

Edlci

12. PVC Connection Status 1 Field What It Indicates

MgmtPVCName

Status What It Indicates

12. PVC Connection Status 2 Field

Network Timeslot Assignment Status Screen Example

Time Slot Assignment Status

Displaying Network Time Slot Assignments

Main Menu → Status→ Timeslot Assignment Status → Network

DSX-1 Timeslot Assignment Status Screen Example

Cross Connect Status Field bottom Indicates

Displaying DSX-1 Time Slot Assignments

Main Menu → Status→ Timeslot Assignment Status→ DSX-1

DBM Interface Status Screen Example

DBM Interface Status

Main Menu → Status→ DBM Interface Status

Invalid Call ID is displayed

13. DBM Interface Status 1 Field What It Indicates

Delivered In Est Chnl-7

Link Name Disabled

13. DBM Interface Status 2 Field What It Indicates

Awarded and Being

Chnl-7

13. DBM Interface Status 3 Field What It Indicates

Value is Call Awarded

Being Delivered In Est

Most Recent and Previous Cause Value Messages

Make sure the network is

Operation and Maintenance

Normal class applies for this

Correct number

Operation and Maintenance

15. IP Routing Table Values 1 Column What It Indicates

IP Routing Table

Main Menu → Status→ IP Routing Table

IP Routing Table Screen Example

TTL

15. IP Routing Table Values 2 Column What It Indicates

Performance Statistics Menu

Performance Statistics

Main Menu → Status→ Performance Statistics

Clearing Performance Statistics

17, SLV Performance Statistics for IP Enabled Dlci

Service Level Verification Performance Statistics

Verification Options, in , Configuration Options, must

Verification Options, in , Configuration Options, over

COS ID

Service Definitions in , Configuration Options

Size is changed, a new average is not available until a new

18. Dlci Performance Statistics 1 What It Indicates

Dlci Performance Statistics

Main Menu → Status → Performance Statistics→ Dlci

18. Dlci Performance Statistics 2 What It Indicates

Additional Performance Statistics for IP Enabled Dlci

20. Frame Relay Performance Statistics 1 What It Indicates

Frame Relay Performance Statistics

Main Menu → Status → Performance Statistics→ Frame Relay

For FrameSaver units with an Isdn DBM

20. Frame Relay Performance Statistics 2 What It Indicates

Frame Relay Errors

Frame Relay LMI

20. Frame Relay Performance Statistics 3 What It Indicates

20. Frame Relay Performance Statistics 4 What It Indicates

Frame Relay Hdlc Errors

To select intervals You must enter an interval or time on

ESF Line Performance Statistics

Main Menu → Status → Performance Statistics→ ESF Line

Lofc

ESF Line Performance Statistics Screen Example

Lofc

UAS

22. DBM Call Performance Statistics What It Indicates

DBM Call Performance Statistics

23. Ethernet Performance Statistics What It Indicates

Ethernet Performance Statistics

Main Menu → Status → Performance Statistics → Ethernet

Trap Event Log Screen Example

Trap Event Log

Main Menu → Status → Trap Event Log

Main Menu → Control→ Disable Modem PassThru to COM

Activating the Modem PassThru Feature

Canceling Modem PassThru Operation

Main Menu → Control→ Enable Modem PassThru to COM

Main Menu → Control→ Disconnect Modem

Manually Disconnecting the Modem

Verifying Modem Operation

Isdn DBM Operation

Forcing Backup Disruptive

If the Result is Then

Placing a Test Call Nondisruptive

Main Menu→ Test→ Isdn Call/PVC Tests

System Operational should appear

Verifying That Backup Can Take Place

Verifying Isdn Lines

FTP File Transfers

Command Definition

If the message displayed is Then

Upgrading System Software

Main Menu → Status→ Identity

Upgrading Isdn BRI DBM Software

Main Menu → Control→ Select Software Release

Determining Whether a Download Is Completed

Changing Software

If retrieving Hen

Transferring Collected Data

Main Menu → Control→ System Alarm Relay Cut-Off

Turning Off the System Alarm Relay

Operation and Maintenance September

Troubleshooting

Main Menu → Status → Display LEDs and Control LEDs

Problem Indicators

Indicators See

Operation and Maintenance

Resetting the Unit By Cycling the Power

Resetting the Unit and Restoring Communication

Resetting the Unit from the Control Menu

If selecting He following occurs

Restoring Communication with an Improperly Configured Unit

LMI Packet Capture Utility Feature

Troubleshooting Management Link Feature

LMI Trace Log Example

LMI Packet Capture Utility→ Display LMI Trace Log

Menu → Control → Reset Device

Alarms

Alarm Conditions 1 What It Indicates What To Do

IPAddress

Alarm Conditions 2 What It Indicates What To Do

Main Menu → Configuration → Isdn → Link Profiles

Name

Link

Alarm Conditions 3 What It Indicates What To Do

Menu→ Configuration→

LMI Down, frame relay

DTE

Alarm Conditions 4 What It Indicates What To Do

PathIP Address

Alarm Conditions 5 What It Indicates What To Do

Nnnn , frame relay

Alarm Conditions 6 What It Indicates What To Do

Alarm Conditions 7 What It Indicates What To Do

Viewing the Trap Event Log

Troubleshooting Tables

Device Problems

Device Problems 1 Symptom Possible Cause Solutions

Improperly Configured Unit on

Device Problems 2 Symptom Possible Cause Solutions

Frame Relay PVC Problems Symptom Possible Cause Solutions

Frame Relay PVC Problems

Main Menu → Status → DBM Interface Status

Isdn DBM Problems

Isdn DBM Problems Symptom Possible Cause Solutions

Test Menu Example

Tests Available

DBM Tests

Test Timeout Feature

Starting and Stopping a Test

When the status of a test is Only command available is

Aborting All Tests

PVC Tests Screen Example

PVC Tests

Main Menu → Test→ Isdn Call/PVC Tests

PVC Loopback

Main Menu → Test→ Network PVC Test

Main Menu → Test→ Data Port PVC Tests

Isdn Call/PVC Tests

Send Pattern

Monitor Pattern

Network PVC Tests/Data Port PVC Tests

Test Call

Connectivity

Physical Tests Screen Example

Physical Tests

LLB

Line Loopback

Main Menu → Test→ Network Physical Tests

PLB

Payload Loopback

RLB AIS

Repeater Loopback

Dtlb DTE

DTE Loopback

Main Menu → Test→ Data Port Physical Tests

DSX

Send Line Loopback

Data Channel Loopbacks on a Frame Relay Link

Main Menu → Test→ Network Physical Tests/PRI Physical Tests

Send Remote Line Loopback

Qrss

Send and Monitor Pattern Tests

Ping Screen Example

IP Ping Test

Target IP Address

Ping Options 1

Packet Size

Inter-Ping Delay

Ping Options 2

Source IP Address

Ping Responses Field Possible Values Description

Response Timeout

Ping Options 3

Main Menu → Test→ IP Ping

IP Ping Test Procedure

Main Menu → Test→ Lamp Test

Lamp Test

His chapter includes

OpenLane Support of FrameSaver Devices

Setting Up the OpenLane SLM System

Setting Up FrameSaver Support

To Find Your License Key Number

Ordering SLM Feature Set Activations

Activation Certificate

Administering and Managing SLM Activations

Checking Activation Certificate Status

Entering an Activation Certificate

Scheduling Activations

Checking the Status of Scheduled Activations

Canceling Scheduled Activations

Accessing and Printing the Certificate Summary Report

9128-A2-GB20-80

10-1

Setting Up NetScout Manager Plus for FrameSaver Devices

Properties

Alarms

Preparation

10-2

10-3

Configuring NetScout Manager Plus

10-4

10-5

Verifying Domains and Groups

10-6

Correcting Domains and Groups

10-7

Property Description Setting

10-8

Adding SLV Alarms Using a Template

10-9

Editing Alarms

10-10

10-11

Adding SLV Alarms Manually

Paradyne

10-12

Field Select or Enter

10-13

Creating History Files

Change 1.3.6.1.2.1.10.32.2.1.6.@IFN.@DLCI to

10-14

10-15

Installing the User-Defined History Files

Dvuhist -f Dallas51 3 config 30 60 Dallas51k.udh

Dvuhist -f Dallas51 301 3 config 30 60 Dallas301.udh

10-16

Monitoring a DLCI’s History Data

10-17

10-18

Monitoring the Agent Using NetScout Manager Plus

10-19

Traffic Statistics Protocol Statistics

Statistical Windows Supported

10-20

11-1

Setting Up Network Health for FrameSaver Devices

11-2

Installation and Setup of Network Health

11-3

Discovering FrameSaver Elements

11-4

Configuring the Discovered Elements

11-5

Grouping Elements for Reports

11-6

About Service Level Reports

Generating Reports for a Group

About At-a-Glance Reports

11-7

Reports Applicable to SLV Devices

About Trend Reports

Printed Reports

11-8

FrameSaver SLV Plus At-a-Glance Report

11-9

11-10

Menus

Menu Hierarchy

Status

Easy Install

Menu Hierarchy September

Snmp MIBs and Traps, and Rmon Alarm Defaults

Downloading MIBs and Snmp Traps

MIB Support

FrameSaver Unit’s sysObjectID system

System Group mib-2

Interfaces Group mib-2

FrameSaver Unit’s sysDescr system

Frame Relay Logical Layer

Profile Link Name

NAM

FR DTE T1 FR NAM

FR Service T1 FR NAM

NetScout Indexes to the Interface Table ifTable

Number Dlci number DTE

Rmon Logical Layer

IfName of the interface

Number Dlci number ALL

Examples

Standards Compliance for Snmp Traps

Variable-Binding

Trap authenticationFailure

Trap warmStart

Table B-3. warmStart Trap What It Indicates Possible Cause

Traps linkUp and linkDown

Strings

Physical Sublayer

PRI

MIB

Logical Link Sublayer

BRI

Xxx.xxx.xxx.xxx , COS nn

Traps enterprise-Specific

‘Path xxx.xxx.xxx.xxx Up

Nnnn ’

That the secondary clock source

Traps RMON-Specific

Standard Dial Control MIB

Trap dialControl

Dial Control Extension MIB

Rmon Alarm and Event Defaults

Event Defaults

EventIndex EventDescription EventType EventCommunity

Rising Event Operation

Physical Interface Alarm Defaults

Frame Relay Link Alarm Defaults

Snmp MIBs and Traps, and Rmon Alarm Defaults

MIB FR DTE MIB RFC

Dlci Alarm Defaults Paradyne Area

Dlci Alarm Defaults NetScout Area

OID

Rx Dlci Link

Object ID Cross-References Numeric Order

MIB Rmon II RFC

6.1.2.1.2.2.1

6.1.2.1.2.10.32.2.1

6.1.2.1.16.12.2.1

CIR

6.1.4.1.1795.2.24.2

6.1.4.1.1795.2.24.2.6.9.4

Dlci CIR

Dlci EIR

6.1.4.1.1795.2.24.2.6.9.4.7.1

6.1.4.1.1795.2.24.2.6.9.4.4.2

6.1.4.1.1795.2.24.2.6.9.4.5.2.1

6.1.4.1.1795.2.24.2.6.9.4.10.3.1

6.1.2.1.10.32.2.1

6.1.2.1.10.18.9.1

6.1.4.1.1795.2.24.2.6.9.4

6.1.4.1.1795.2.24.2.6.9.4

Xxxxxxxxxxxx

CLI Commands

Convention Meaning

X.x

Router CLI Commands, Codes, and Designations

Table C-2. Access Control Commands

Pager Command

Access Control Commands

Table C-1. Pager Command

Example configure terminal

Configuration Commands

Table C-3. Configuration Commands

Configure terminal factory

Example interface serial 132.53.4.2

Interface Commands

Table C-4. Interface Commands 1

Command Mode config, config-if, config-subif

Example encapsulation frame-relay ietf

Table C-4. Interface Commands 2

Encapsulation encapsulation-type encapsulation-protocol

Example ip address 132.53.4.2

Example ip unnumbered

Table C-4. Interface Commands 3

No ip unnumbered null

No frame-relay interface-dlci dlci-num

No ip multicast-routing

IP Routing Commands

Table C-5. IP Routing Commands

No ip routing

Example bridge crb 1 route ip

Bridge Commands

Table C-6. Bridge Commands 1

Example no bridge-group

Table C-6. Bridge Commands 2

Command Mode config-if, config-subif

No bridge-group bridge-group

Example arp timeout

ARP Commands

Table C-7. ARP Commands

Arp timeout time No arp timeout time

No ip nat inside outside

NAT Commands

Table C-8. NAT Commands 1

Example ip nat translation timeout

No ip nat pool pool-namestart-ip-addr end-ip-addr

Table C-8. NAT Commands 2

Ip nat pool pool-name start-ip-addr end-ip-addr

Netmask netmask prefix-length / prefix-length

From previous

Table C-8. NAT Commands 3

Clear ip nat translation

No ip dhcp pool pool-name

Dhcp Server Commands

Table C-9. Dhcp Server Commands 1

No service dhcp

Dns-server ip-address No dns-server ip-address

Table C-9. Dhcp Server Commands 2

Default-router ip-address No default-router ip-address

Domain-name domain-name No domain-name domain-name

Network network-num

Table C-9. Dhcp Server Commands 3

Example ip dhcp relay max-clients

Dhcp Relay Agent Commands

Table C-10. Dhcp Relay Agent Commands

No ip dhcp-server ip-address

No access-list access-list-numpermit deny

Filter access-list Commands

Table C-11. Filter Commands 1

Access-list access-list-num permit deny

For Extended IP Access Lists

Table C-11. Filter Commands 2

Example access-list 200 permit 0x200 range

Table C-11. Filter Commands 3

For Protocol Type Access Lists

No ip access-group access-list-1-199numin out

Table C-11. Filter Commands 4

Table C-12. Diagnostic Commands 1

Diagnostic Commands

Traceroute protocol dest-ipsource source-ip length bytes

Table C-12. Diagnostic Commands 2

Show arp

Show Commands

Table C-13. Show Commands 1

Show configuration

Show interface intf-type intf-num .sub-intf-num

Table C-13. Show Commands 2

Show configuration saved unsaved

Show frame-relay map

Show ip route ip-address

Table C-13. Show Commands 3

Show ip dhcp binding ip-address

Show ip nat translations

Show spanning-tree

Table C-13. Show Commands 4

Show ip traffic

Table C-14. Ethernet Type Codes Hex 1 Description

Ethernet Type Codes

Table C-14. Ethernet Type Codes Hex 2 Description

All 3 n = Destination unreachable

Protocol and Port Designations

Icmp Designations

All 5 n = All redirects

TCP Port Designations

UDP Port Designations

CLI Summaries

Router Command Line Summaries Shortcuts

Intf-type intf-num .sub-intf-num

Show Command Summary

Table D-1. Show Commands Function

Table D-2. Access Control and System Level Commands Function

Access Control and System Level Command Summary

Dns-serverip-address

CLI Command Summary

Table D-3. CLI Commands 1

Clear counters intf-type intf-num .sub-intf-num

Encapsulation encapsulation-type encapsulation-protocol

Table D-3. CLI Commands 2

CLI Command Default Settings

Rear Panels

Connectors, Cables, and Pin Assignments

Connectors, Cables, and Pin Assignments

Model

COM Port for 9126 and 9128-II 25-Position

COM Port Connector

Signal Direction Pin #

Pin # Signal Direction

Modular Plug DB9 Socket

COM Port-to-PC Cable Feature No -F2-550

COM Port for 9128-II Carrier Mount

COM Port Non-Keyed Position

Position Modular Plug DB25 Plug

COM Port-to-Terminal/Printer Cable Feature No -F2-540

COM Port Non-Keyed

Cisco 2500 Series Router RJ45 Jack

COM Port AUX Port Signal DB25 Pin # Direction RJ45 Pin #

COM Port AUX Port Signal DB25 Pin # Direction

COM Port-to-Router Cables

3COM Router DB9 Socket

COM Port Console Port Signal DB25 Pin # Direction DB9 Pin #

COM Port AUX Port Signal RJ45 Pin # Direction

COM Port AUX Port Signal RJ45 Pin # Direction DB25 Pin #

DTR RTS

Gender Adapter/Changer

LAN Adapter Converter and Cable

Plug-to-Modular Jack Converter Com Port Position DB25 Plug

Direction Pin Socket

DTE Port Connector

Pin

Standard V.35 Straight-through Cable

Standard V.35 Crossover Cable

MM NN

Position DB15 Modular Plug Socket Unkeyed

DSX-1 Connector

DSX-1 Adapter Feature No -F1-560

Function Circuit Direction Pin Number

DSX-1 Port for 1-Slot 9128-II 15-Position

Function Circuit Line # Pin #

T1 Network Cable Feature No -F1-500

T1 Mass Termination Cable Feature No -F1-500

Plug Unkeyed

Ethernet Port Connector

Canadian T1 Line Interface Cable Feature No -F1-510

Isdn Modular Cable

Modem Connector

Isdn DBM Connector

Connectors, Cables, and Pin Assignments September

Physical Environment

Table F-1. NAM Technical Specifications 1 Criteria

Physical Dimensions

Approvals

Table F-1. NAM Technical Specifications 2 Criteria

Ethernet Port

Table F-1. NAM Technical Specifications 3 Criteria

Isdn PRI DBM Interface

B8ZS

Power Consumption Dissipation

Ethernet Port FrameSaver

Isdn BRI DBM Interface

BRI, NI-1

Heat Dissipation Max

AC Power Requirements

Typical Power Consumption

Standards Compliance

Switch Compatibility

Service Supported

Switched Network Interface

Line Build-Out LBO

Framing Format

Coding Format

FrameSaver SLV Units

Model/Feature

Equipment

Description Number

Equipment List

Isdn PRI DBM

NMS Products

FrameSaver SLM Feature Set Upgrade

Optional Features

Power Supplies

Series Access Carrier 9128-II NAM only

Cables

Description Part Number Feature Number

IN-1

Index

CLI

IN-2

Becn

Dhcp

IN-3

DBM

IN-4

EIR

IN-5

EER

IN-6

IP SLV

IN-7

LAN

LOS

IN-8

LOF

NMS

IN-9

OID

IN-10

Port

IN-11

IN-12

IN-13

IN-14

IN-15

IN-16