LSI Specification | MB86617A |

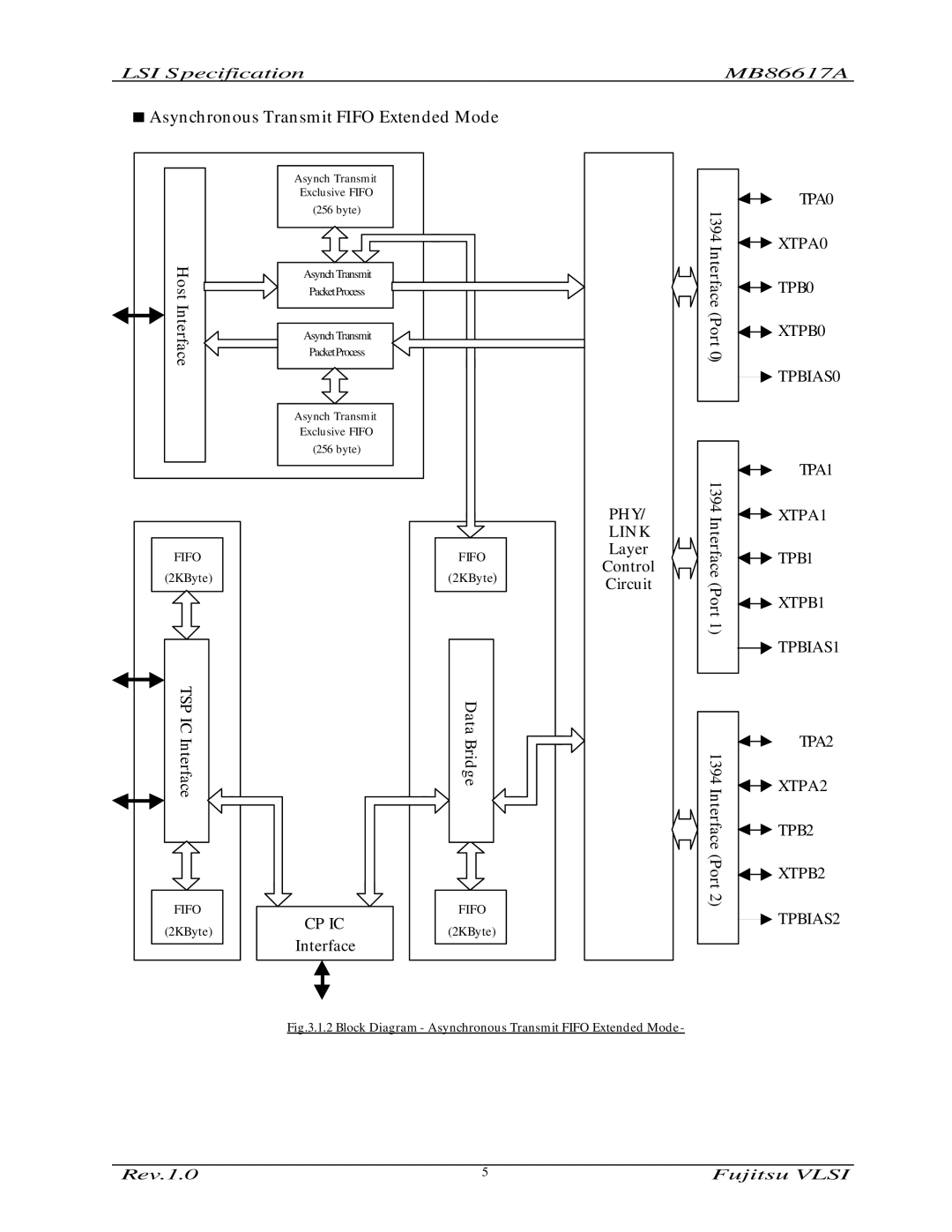

<Asynchronous Transmit FIFO Extended Mode

| Asynch Transmit |

| Exclusive FIFO |

| (256 byte) |

Host | Asynch Transmit |

PacketProcess | |

Interface | Asynch Transmit |

PacketProcess | |

| |

| Asynch Transmit |

| Exclusive FIFO |

| (256 byte) |

FIFO |

| FIFO | |

(2KByte) |

| (2KByte) | |

TSP IC |

| Data | |

Interface |

| Bridge | |

FIFO | CP IC | FIFO | |

(2KByte) | (2KByte) | ||

Interface | |||

|

|

PHY/

LINK

Layer

Control

Circuit

1394 Interface (Port 0)

1394 Interface (Port 1)

1394 Interface (Port 2)

TPA0

![]()

![]() XTPA0

XTPA0

![]()

![]() TPB0

TPB0

![]()

![]() XTPB0

XTPB0

![]() TPBIAS0

TPBIAS0

TPA1

![]()

![]() XTPA1

XTPA1

![]()

![]() TPB1

TPB1

![]()

![]() XTPB1

XTPB1

![]() TPBIAS1

TPBIAS1

TPA2

![]()

![]() XTPA2

XTPA2

![]()

![]() TPB2

TPB2

![]()

![]() XTPB2

XTPB2

![]() TPBIAS2

TPBIAS2

Fig.3.1.2 Block Diagram - Asynchronous Transmit FIFO Extended Mode-

Rev.1.0 | 5 | Fujitsu VLSI |