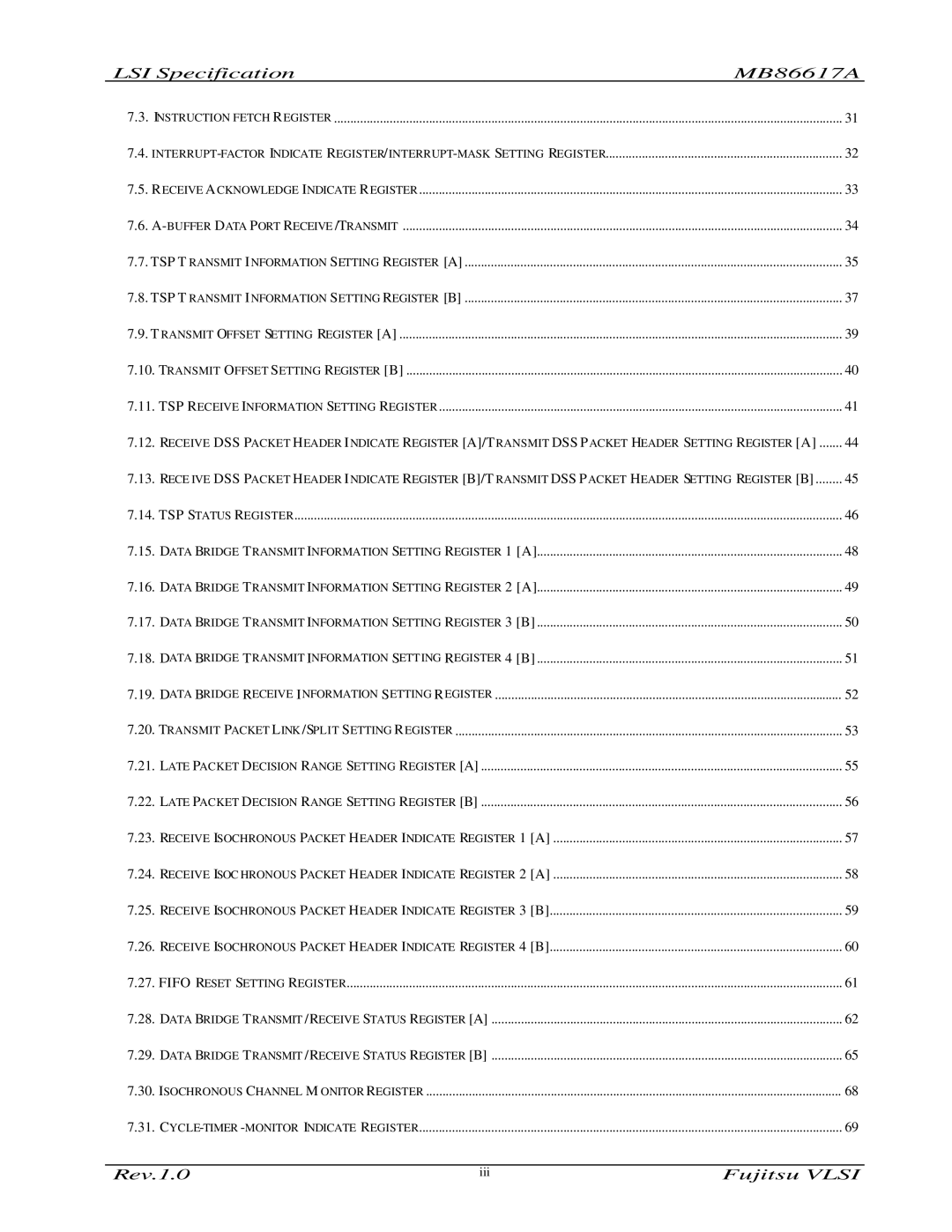

LSI Specification |

| MB86617A | |

7.3. INSTRUCTION FETCH R EGISTER |

| 31 | |

7.4. | 32 | ||

7.5. R ECEIVE A CKNOWLEDGE INDICATE R EGISTER |

| 33 | |

7.6. |

| 34 | |

7.7. TSP T RANSMIT I NFORMATION SETTING REGISTER [A] |

| 35 | |

7.8. TSP T RANSMIT I NFORMATION SETTING REGISTER [B] |

| 37 | |

7.9. T RANSMIT OFFSET SETTING REGISTER [A] |

| 39 | |

7.10. TRANSMIT OFFSET SETTING REGISTER [B] |

| 40 | |

7.11. TSP RECEIVE INFORMATION SETTING REGISTER |

| 41 | |

7.12. RECEIVE DSS PACKET HEADER I NDICATE REGISTER [A]/T RANSMIT DSS P ACKET HEADER SETTING REGISTER [A] | 44 | ||

7.13. RECE IVE DSS PACKET HEADER I NDICATE REGISTER [B]/T RANSMIT DSS P ACKET HEADER SETTING REGISTER [B] | 45 | ||

7.14. TSP STATUS REGISTER |

| 46 | |

7.15. DATA BRIDGE TRANSMIT INFORMATION SETTING REGISTER 1 [A] | 48 | ||

7.16. DATA BRIDGE TRANSMIT INFORMATION SETTING REGISTER 2 [A] | 49 | ||

7.17. DATA BRIDGE TRANSMIT INFORMATION SETTING REGISTER 3 [B] | 50 | ||

7.18. DATA BRIDGE TRANSMIT INFORMATION SETTING REGISTER 4 [B] | 51 | ||

7.19. DATA BRIDGE RECEIVE I NFORMATION SETTING R EGISTER | 52 | ||

7.20. TRANSMIT PACKET LINK /SPLIT SETTING R EGISTER |

| 53 | |

7.21. LATE PACKET DECISION RANGE SETTING REGISTER [A] | .............................................................................................................. | 55 | |

7.22. LATE PACKET DECISION RANGE SETTING REGISTER [B] | .............................................................................................................. | 56 | |

7.23. RECEIVE ISOCHRONOUS PACKET HEADER INDICATE REGISTER 1 [A] | 57 | ||

7.24. RECEIVE ISOC HRONOUS PACKET HEADER INDICATE REGISTER 2 [A] | 58 | ||

7.25. RECEIVE ISOCHRONOUS PACKET HEADER INDICATE REGISTER 3 [B] | 59 | ||

7.26. RECEIVE ISOCHRONOUS PACKET HEADER INDICATE REGISTER 4 [B] | 60 | ||

7.27. FIFO RESET SETTING REGISTER |

| 61 | |

7.28. DATA BRIDGE TRANSMIT /RECEIVE STATUS REGISTER [A] | 62 | ||

7.29. DATA BRIDGE TRANSMIT /RECEIVE STATUS REGISTER [B] | 65 | ||

7.30. ISOCHRONOUS CHANNEL M ONITOR REGISTER |

| 68 | |

7.31. |

| 69 | |

Rev.1.0 | iii | Fujitsu VLSI | |