LSI Specification | MB86617A |

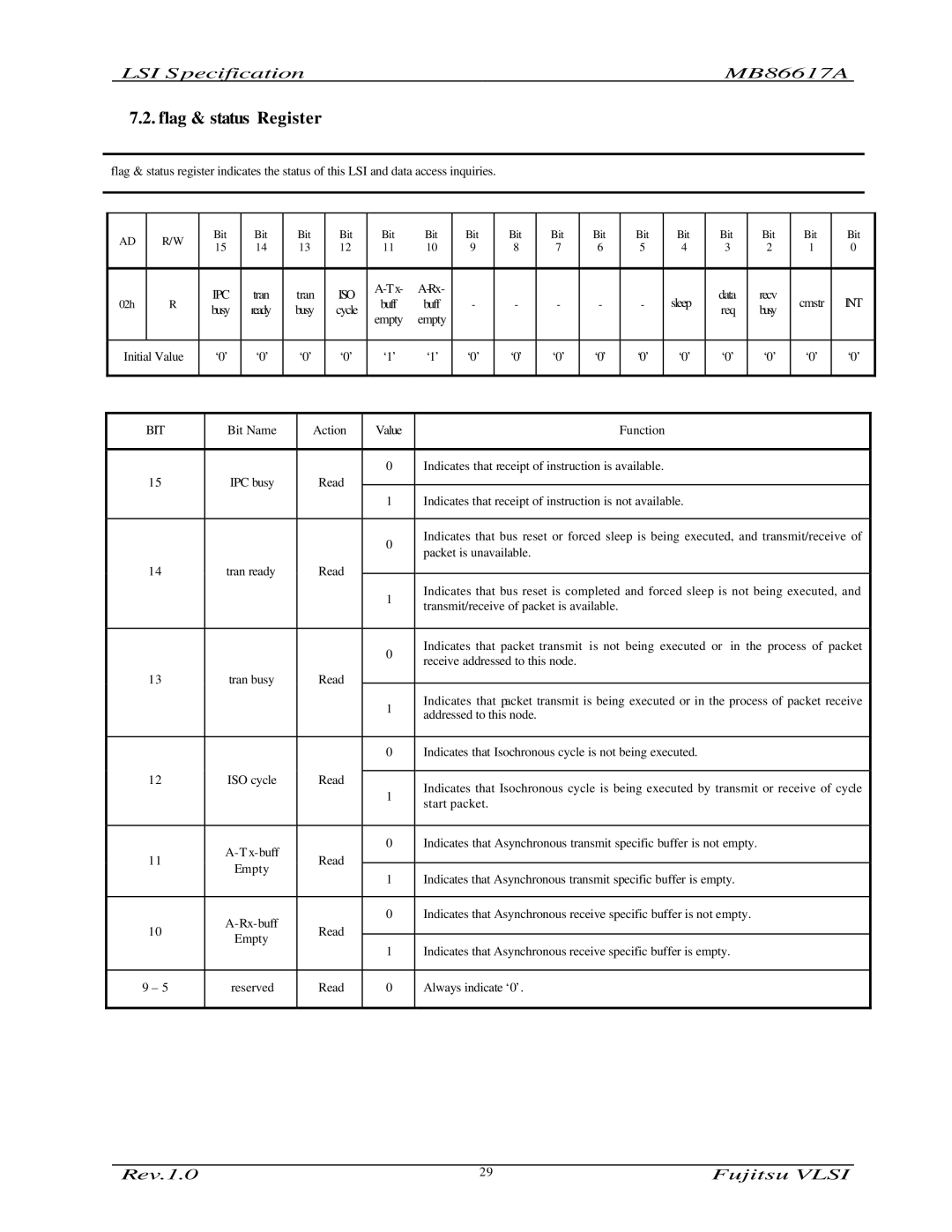

7.2. flag & status Register

flag & status register indicates the status of this LSI and data access inquiries.

AD |

| R/W |

| Bit |

| Bit |

| Bit |

| Bit | Bit | Bit | Bit | Bit |

| Bit |

| Bit | Bit |

| Bit | Bit |

| Bit | Bit | Bit | ||

| 15 |

| 14 | 13 |

| 12 |

| 11 | 10 | 9 | 8 |

| 7 |

| 6 | 5 |

| 4 | 3 |

| 2 | 1 | 0 |

| ||||

|

|

|

|

|

|

|

|

|

|

| ||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| IPC |

| tran |

| tran |

| ISO |

|

|

|

|

|

|

|

| sleep | data |

| recv | cmstr | INT | ||||

02h |

| R |

|

|

|

| buff | buff | - | - |

| - |

| - | - |

|

| |||||||||||

|

| busy |

| ready | busy |

| cycle |

|

|

| req |

| busy | |||||||||||||||

|

|

|

|

|

| empty | empty |

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

Initial Value |

| ‘0’ |

| ‘0’ |

| ‘0’ |

| ‘0’ | ‘1’ | ‘1’ | ‘0’ | ‘0’ |

| ‘0’ |

| ‘0’ | ‘0’ |

| ‘0’ | ‘0’ |

| ‘0’ | ‘0’ | ‘0’ | ||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||

|

| BIT |

| Bit Name |

| Action |

| Value |

|

|

|

|

|

|

| Function |

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||

|

|

|

|

|

|

|

|

|

|

|

| 0 | Indicates that receipt of instruction is available. |

|

|

|

|

|

|

| ||||||||

| 15 |

| IPC busy |

|

| Read |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||

|

|

|

| 1 | Indicates that receipt of instruction is not available. |

|

|

|

|

|

| |||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

| 0 | Indicates that bus reset or forced sleep is being executed, and transmit/receive of |

| ||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

| packet is unavailable. |

|

|

|

|

|

|

|

|

|

|

|

| ||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||

| 14 |

| tran ready |

|

| Read |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||

|

|

|

| 1 | Indicates that bus reset is completed and forced sleep is not being executed, and |

| ||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

| transmit/receive of packet is available. |

|

|

|

|

|

|

|

|

| |||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||||||

|

|

|

|

|

|

|

|

|

|

|

| 0 | Indicates that packet transmit | is not being executed or in the process of packet |

| |||||||||||||

|

|

|

|

|

|

|

|

|

|

|

| receive addressed to this node. |

|

|

|

|

|

|

|

|

|

| ||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||

| 13 |

| tran busy |

|

| Read |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||

|

|

|

|

|

|

|

|

|

|

|

| 1 | Indicates that packet transmit is being executed or in the process of packet receive |

| ||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

| addressed to this node. |

|

|

|

|

|

|

|

|

|

|

|

| ||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||

|

|

|

|

|

|

|

|

|

|

|

| 0 | Indicates that Isochronous cycle is not being executed. |

|

|

|

|

|

| |||||||||

| 12 |

| ISO cycle |

|

| Read |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||

|

|

|

|

|

| Indicates that Isochronous cycle is being executed by transmit or receive of cycle |

| |||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

| 1 |

| |||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

| start packet. |

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||||

|

|

|

|

|

|

|

|

| 0 | Indicates that Asynchronous transmit specific buffer is not empty. |

|

|

|

| ||||||||||||||

| 11 |

|

|

| Read |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||

|

|

| Empty |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

| 1 | Indicates that Asynchronous transmit specific buffer is empty. |

|

|

|

| |||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||||

|

|

|

|

|

|

|

|

| 0 | Indicates that Asynchronous receive specific buffer is not empty. |

|

|

|

| ||||||||||||||

| 10 |

|

|

| Read |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||

|

|

| Empty |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

| 1 | Indicates that Asynchronous receive specific buffer is empty. |

|

|

|

| |||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||

| 9 – 5 |

|

| reserved |

|

| Read |

| 0 | Always indicate ‘0’. |

|

|

|

|

|

|

|

|

|

|

|

| ||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Rev.1.0 | 29 | Fujitsu VLSI |