LSI Specification | MB86617A |

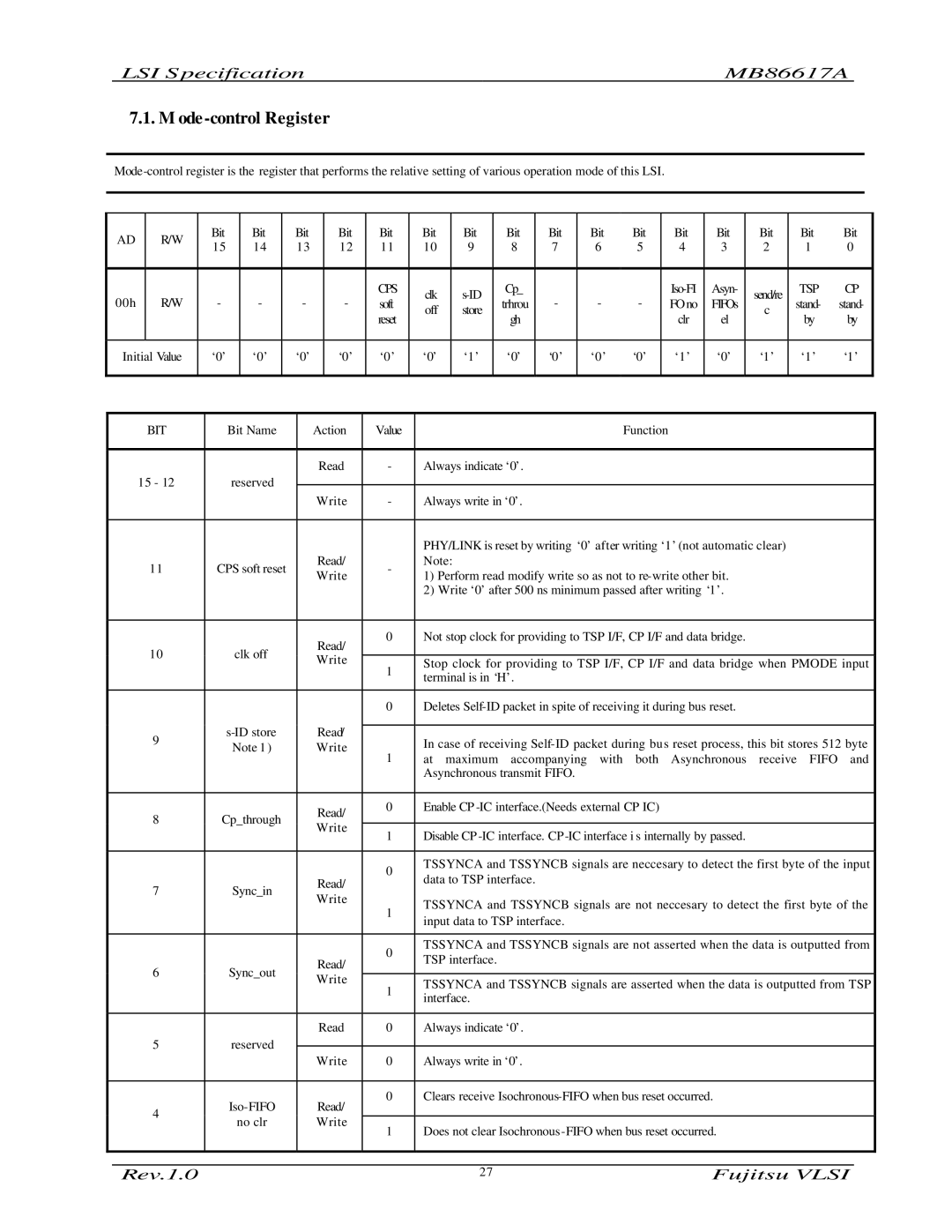

7.1. M ode-control Register

| AD |

| R/W |

| Bit |

| Bit |

| Bit |

| Bit | Bit |

| Bit |

| Bit |

| Bit | Bit | Bit | Bit |

| Bit | Bit |

| Bit | Bit | Bit | |||

|

| 15 |

| 14 |

| 13 |

| 12 |

| 11 | 10 |

| 9 |

| 8 | 7 | 6 | 5 |

| 4 | 3 |

| 2 | 1 | 0 |

| |||||

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

| 00h |

| R/W | - |

| - |

| - |

| - |

| CPS |

| clk |

|

| Cp_ | - | - | - |

| Asyn- |

| send/re | TSP | CP | |||||

|

|

|

|

|

| soft |

|

|

| trhrou |

| FO no | FIFOs |

| stand- | stand- | |||||||||||||||

|

|

|

|

|

|

| off |

| store |

|

|

| c | ||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

| reset |

|

|

| gh |

|

|

|

| clr | el |

| by | by | ||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

| Initial Value |

| ‘0’ |

| ‘0’ |

| ‘0’ |

| ‘0’ | ‘0’ |

| ‘0’ |

| ‘1’ |

| ‘0’ | ‘0’ | ‘0’ | ‘0’ |

| ‘1’ | ‘0’ |

| ‘1’ | ‘1’ | ‘1’ | |||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||

|

|

| BIT |

|

| Bit Name |

|

| Action |

| Value |

|

|

|

|

|

|

|

| Function |

|

|

|

|

|

|

| ||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

|

|

| Read |

| - |

| Always indicate ‘0’. |

|

|

|

|

|

|

|

|

|

|

| |||||

|

| 15 - 12 |

|

| reserved |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||

|

|

|

|

|

| Write |

| - |

| Always write in ‘0’. |

|

|

|

|

|

|

|

|

|

|

| ||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| PHY/LINK is reset by writing ‘0’ after writing ‘1’ (not automatic clear) |

|

|

| ||||||||||||

|

| 11 |

| CPS soft reset |

|

| Read/ |

| - |

| Note: |

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||

|

|

|

|

| Write |

|

| 1) Perform read modify write so as not to |

|

|

|

| |||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 2) Write ‘0’ after 500 ns minimum passed after writing ‘1’. |

|

|

|

| |||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||||

|

|

|

|

|

|

|

|

|

|

| Read/ |

| 0 |

| Not stop clock for providing to TSP I/F, CP I/F and data bridge. |

|

|

|

| ||||||||||||

|

| 10 |

|

| clk off |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

| Write |

| 1 |

| Stop clock for providing to TSP I/F, CP I/F and data bridge when PMODE input | |||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| terminal is in ‘H’. |

|

|

|

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

| 0 |

| Deletes |

|

|

|

| |||||||||||

|

| 9 |

|

|

|

| Read/ |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

| In case of receiving | ||||||||||||||||||||||

|

|

|

| Note 1) |

|

| Write |

| 1 |

| |||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| at maximum accompanying with both Asynchronous receive FIFO and | ||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| Asynchronous transmit FIFO. |

|

|

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||

|

| 8 |

| Cp_through |

|

| Read/ |

| 0 |

| Enable CP |

|

|

|

|

|

|

| |||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||

|

|

|

|

| Write |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||

|

|

|

|

|

|

|

|

|

|

|

| 1 |

| Disable CP |

|

|

|

| |||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

| 0 |

| TSSYNCA and TSSYNCB signals are neccesary to detect the first byte of the input | |||||||||||||||

|

|

|

|

|

|

|

|

|

|

| Read/ |

|

| data to TSP interface. |

|

|

|

|

|

|

|

|

|

|

| ||||||

|

| 7 |

|

| Sync_in |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||

|

|

|

|

|

| Write |

|

|

| TSSYNCA and TSSYNCB signals are not neccesary to detect the first byte of the | |||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

| 1 |

| ||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| input data to TSP interface. |

|

|

|

|

|

|

|

|

|

| ||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

| 0 |

| TSSYNCA and TSSYNCB signals are not asserted when the data is outputted from | |||||||||||||||

|

|

|

|

|

|

|

|

|

|

| Read/ |

|

| TSP interface. |

|

|

|

|

|

|

|

|

|

|

|

| |||||

|

| 6 |

|

| Sync_out |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||

|

|

|

|

|

| Write |

| 1 |

| TSSYNCA and TSSYNCB signals are asserted when the data is outputted from TSP | |||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| interface. |

|

|

|

|

|

|

|

|

|

|

|

| ||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

|

|

| Read |

| 0 |

| Always indicate ‘0’. |

|

|

|

|

|

|

|

|

|

|

| |||||

|

| 5 |

|

| reserved |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||

|

|

|

|

|

| Write |

| 0 |

| Always write in ‘0’. |

|

|

|

|

|

|

|

|

|

|

| ||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||||

|

|

|

|

|

|

|

| Read/ |

| 0 |

| Clears receive |

|

|

|

| |||||||||||||||

|

| 4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||

|

|

|

| no clr |

|

| Write |

| 1 |

| Does not clear Isochronous |

|

|

|

| ||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| Rev.1.0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

| 27 |

|

|

|

|

|

|

| Fujitsu VLSI | |||||||