LSI Specification | MB86617A |

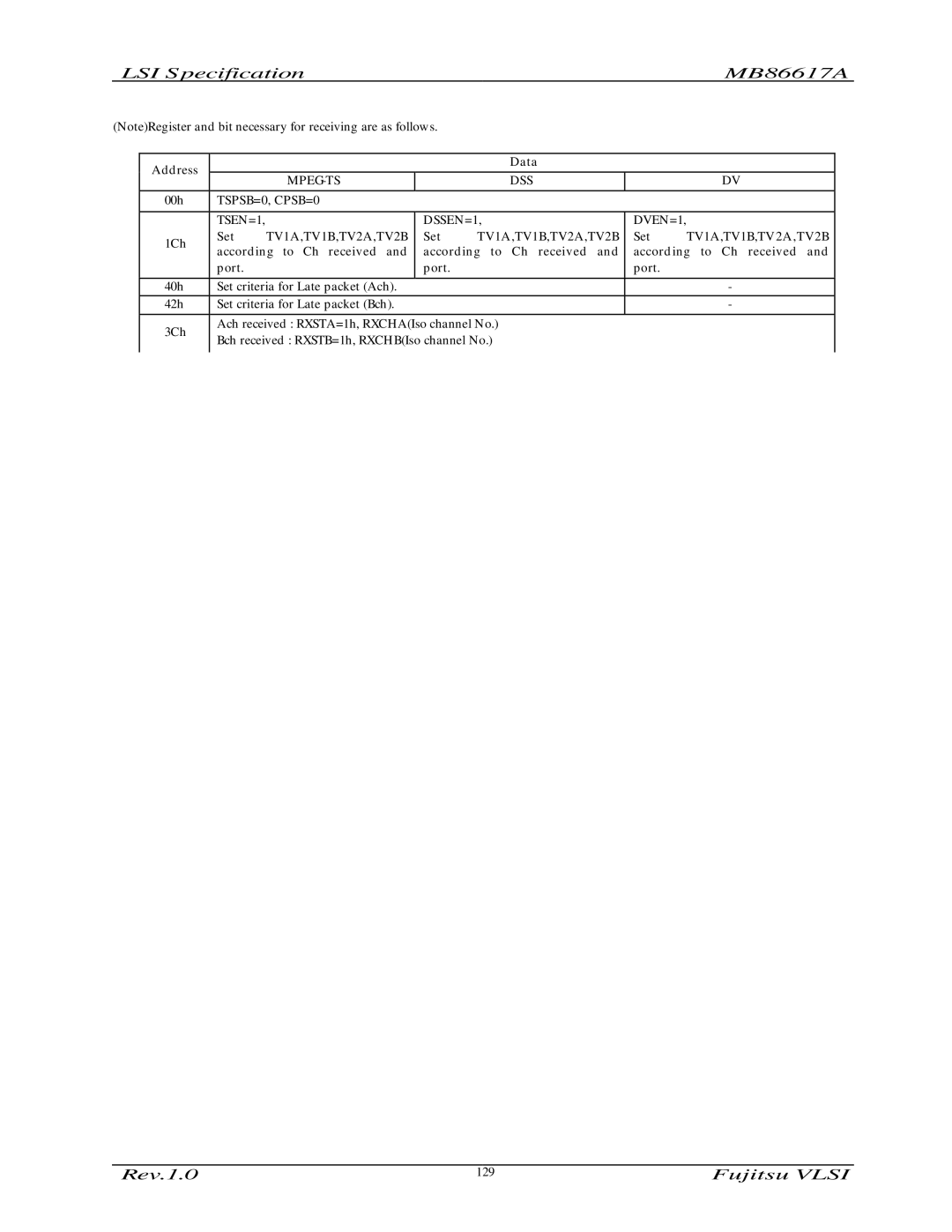

(Note)Register and bit necessary for receiving are as follows.

Address |

|

|

| Data |

|

| |

|

|

| DSS |

| DV | ||

00h | TSPSB=0, CPSB=0 |

|

|

|

| ||

|

|

|

|

|

| ||

| TSEN=1, |

| DSSEN=1, | DVEN=1, |

| ||

1Ch | Set | TV1A,TV1B,TV2A,TV2B | Set | TV1A,TV1B,TV2A,TV2B | Set | TV1A,TV1B,TV2A,TV2B | |

according to Ch received and | according to Ch received and | according to Ch received and | |||||

| |||||||

| port. |

| port. |

| port. |

| |

|

|

|

|

|

| ||

40h | Set criteria for Late packet (Ach). |

|

|

| - | ||

42h | Set criteria for Late packet (Bch). |

|

|

| - | ||

3Ch | Ach received : RXSTA=1h, RXCHA(Iso channel No.) |

|

| ||||

Bch received : RXSTB=1h, RXCHB(Iso channel No.) |

|

| |||||

|

|

| |||||

|

|

|

|

|

|

| |

Rev.1.0 | 129 | Fujitsu VLSI |