LSI Specification | MB86617A |

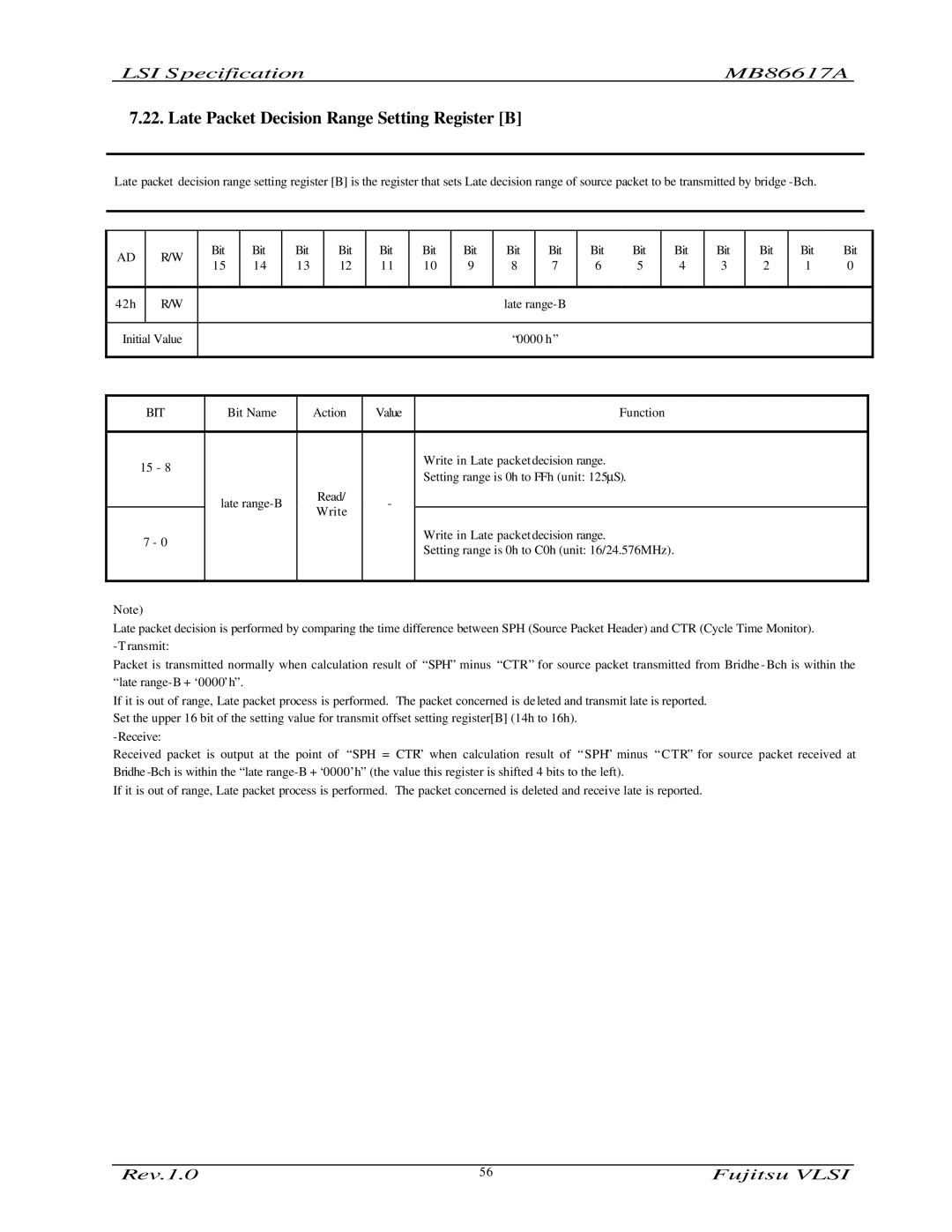

7.22. Late Packet Decision Range Setting Register [B]

Late packet decision range setting register [B] is the register that sets Late decision range of source packet to be transmitted by bridge

AD |

| R/W |

| Bit |

| Bit |

| Bit |

| Bit | Bit |

| Bit | Bit | Bit | Bit | Bit | Bit |

| Bit | Bit | Bit | Bit | Bit | |||

| 15 |

| 14 |

| 13 |

| 12 |

| 11 | 10 | 9 | 8 | 7 | 6 | 5 |

| 4 | 3 | 2 | 1 | 0 |

| |||||

|

|

|

|

|

|

|

|

| |||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

42h |

| R/W |

|

|

|

|

|

|

|

|

|

|

|

|

|

| late |

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

Initial Value |

|

|

|

|

|

|

|

|

|

|

|

|

|

| “0000 h ” |

|

|

|

|

|

|

|

|

| |||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||

|

| BIT |

|

| Bit Name |

|

| Action |

| Value |

|

|

|

|

|

| Function |

|

|

|

|

|

| ||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||

| 15 - 8 |

|

|

|

|

|

|

|

|

|

|

|

| Write in Late packet decision range. |

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

|

|

|

|

| Setting range is 0h to FFh (unit: 125μS). |

|

|

|

|

|

| ||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||

|

|

|

| late |

|

| Read/ |

| - |

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||

|

|

|

|

|

| Write |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

| 7 - 0 |

|

|

|

|

|

|

|

|

|

|

|

| Write in Late packet decision range. |

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

|

|

|

|

| Setting range is 0h to C0h (unit: 16/24.576MHz). |

|

|

|

|

|

| ||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Note)

Late packet decision is performed by comparing the time difference between SPH (Source Packet Header) and CTR (Cycle Time Monitor).

Packet is transmitted normally when calculation result of “SPH” minus “CTR” for source packet transmitted from Bridhe - Bch is within the “late

If it is out of range, Late packet process is performed. The packet concerned is deleted and transmit late is reported. Set the upper 16 bit of the setting value for transmit offset setting register[B] (14h to 16h).

Received packet is output at the point of “SPH = CTR” when calculation result of “ SPH” minus “ CTR” for source packet received at Bridhe

If it is out of range, Late packet process is performed. The packet concerned is deleted and receive late is reported.

Rev.1.0 | 56 | Fujitsu VLSI |