LSI Specification | MB86617A |

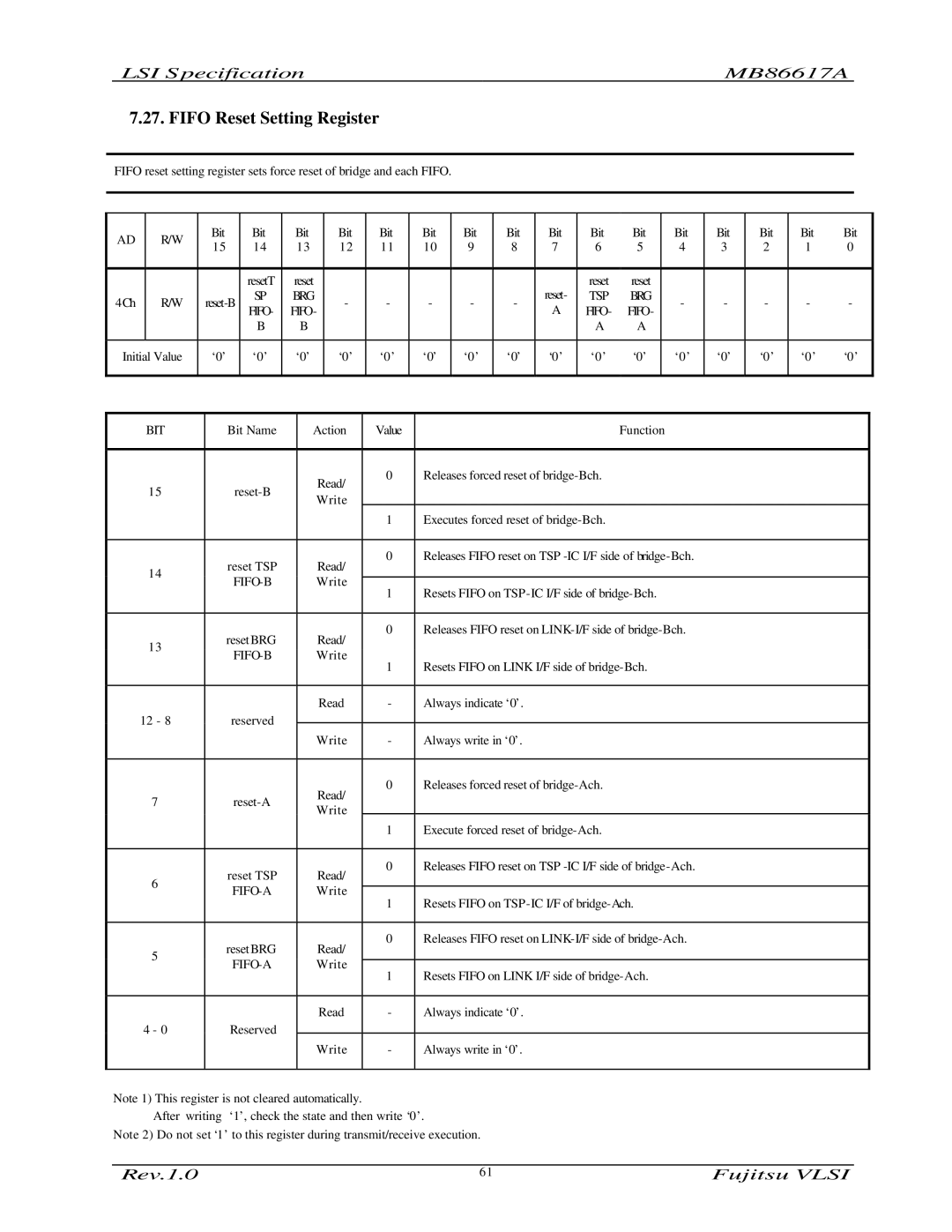

7.27. FIFO Reset Setting Register

FIFO reset setting register sets force reset of bridge and each FIFO.

AD |

| R/W |

| Bit |

| Bit | Bit |

|

| Bit | Bit |

| Bit | Bit | Bit | Bit | Bit | Bit |

| Bit | Bit | Bit | Bit | Bit | ||

| 15 |

| 14 | 13 |

|

| 12 |

| 11 | 10 | 9 | 8 | 7 | 6 | 5 |

| 4 | 3 | 2 | 1 | 0 | |||||

|

|

|

|

|

|

|

| |||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

| resetT | reset |

|

|

|

|

|

|

|

| reset- | reset | reset |

|

|

|

|

|

| ||

4Ch |

| R/W |

| SP | BRG |

|

| - |

| - | - | - | - | TSP | BRG |

| - | - | - | - | - | |||||

|

| FIFO- | FIFO- |

|

| A | FIFO- | FIFO- |

| |||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||

|

|

|

|

|

| B |

| B |

|

|

|

|

|

|

|

|

|

| A | A |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

Initial Value |

| ‘0’ |

| ‘0’ | ‘0’ |

|

| ‘0’ | ‘0’ |

| ‘0’ | ‘0’ | ‘0’ | ‘0’ | ‘0’ | ‘0’ |

| ‘0’ | ‘0’ | ‘0’ | ‘0’ | ‘0’ | ||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||

|

| BIT |

|

| Bit Name |

|

| Action |

| Value |

|

|

|

|

|

| Function |

|

|

|

|

| ||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||

|

|

|

|

|

|

|

|

|

| Read/ |

| 0 |

| Releases forced reset of |

|

|

|

|

|

|

| |||||

| 15 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||

|

|

|

|

| Write |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||

|

|

|

|

|

|

|

|

|

|

|

|

| 1 |

| Executes forced reset of |

|

|

|

|

|

|

| ||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||

|

|

|

|

| reset TSP |

|

|

| Read/ |

| 0 |

| Releases FIFO reset on TSP |

|

|

|

| |||||||||

| 14 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||

|

|

|

|

| Write |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||

|

|

|

|

|

|

|

| 1 |

| Resets FIFO on |

|

|

|

|

| |||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||

|

|

|

|

| reset BRG |

|

|

| Read/ |

| 0 |

| Releases FIFO reset on |

|

|

|

| |||||||||

| 13 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||

|

|

|

|

| Write |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||

|

|

|

|

|

|

|

| 1 |

| Resets FIFO on LINK I/F side of |

|

|

|

|

| |||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||

|

|

|

|

|

|

|

|

|

| Read |

| - |

| Always indicate ‘0’. |

|

|

|

|

|

|

|

|

| |||

| 12 - 8 |

|

| reserved |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

|

|

|

|

| Write |

| - |

| Always write in ‘0’. |

|

|

|

|

|

|

|

|

| ||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||

|

|

|

|

|

|

|

|

|

| Read/ |

| 0 |

| Releases forced reset of |

|

|

|

|

|

|

| |||||

| 7 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||

|

|

|

|

| Write |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||

|

|

|

|

|

|

|

|

|

|

|

|

| 1 |

| Execute forced reset of |

|

|

|

|

|

|

| ||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||

|

|

|

|

| reset TSP |

|

|

| Read/ |

| 0 |

| Releases FIFO reset on TSP |

|

|

|

| |||||||||

| 6 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||

|

|

|

|

| Write |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||

|

|

|

|

|

| 1 |

| Resets FIFO on |

|

|

|

|

| |||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||

|

|

|

|

| reset BRG |

|

|

| Read/ |

| 0 |

| Releases FIFO reset on |

|

|

|

| |||||||||

| 5 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||

|

|

|

|

| Write |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||

|

|

|

|

|

|

|

| 1 |

| Resets FIFO on LINK I/F side of |

|

|

|

|

| |||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||

|

|

|

|

|

|

|

|

|

| Read |

| - |

| Always indicate ‘0’. |

|

|

|

|

|

|

|

|

| |||

| 4 - 0 |

|

| Reserved |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

|

| Write |

| - |

| Always write in ‘0’. |

|

|

|

|

|

|

|

|

| ||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Note 1) This register is not cleared automatically.

After writing ‘1’, check the state and then write ‘0’.

Note 2) Do not set ‘1’ to this register during transmit/receive execution.

Rev.1.0 | 61 | Fujitsu VLSI |