LSI Specification | MB86617A |

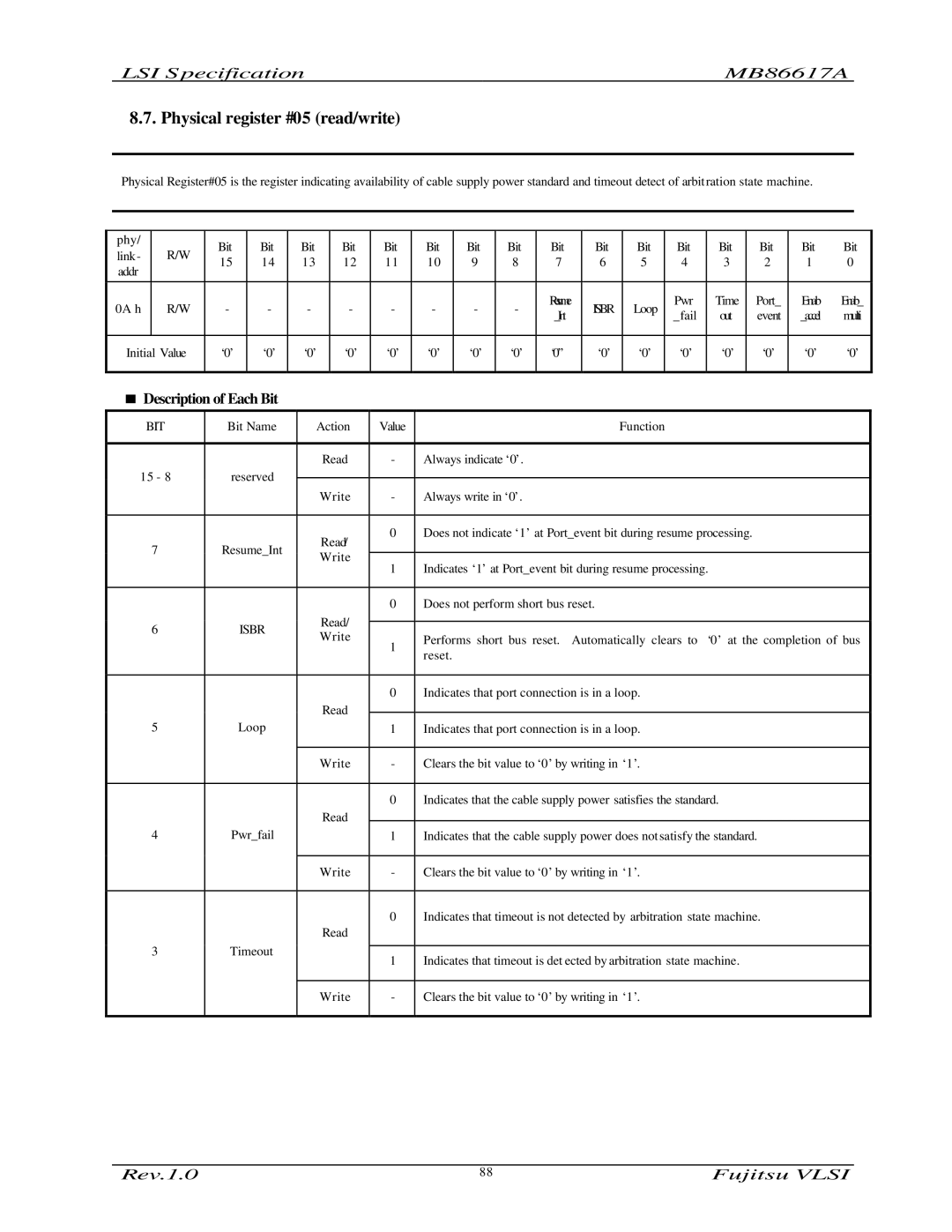

8.7. Physical register #05 (read/write)

Physical Register#05 is the register indicating availability of cable supply power standard and timeout detect of arbitration state machine.

phy/ |

| Bit | Bit | Bit | Bit | Bit | Bit | Bit | Bit | Bit | Bit | Bit | Bit | Bit | Bit | Bit | Bit | |

link- | R/W | |||||||||||||||||

15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |||

addr |

| |||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

0A h | R/W | - | - | - | - | - | - | - | - | Resume | ISBR | Loop | Pwr | Time | Port_ | Enab | Enab_ | |

_Int | _fail | out | event | _accel | multi | |||||||||||||

|

|

|

|

|

|

|

|

|

|

|

| |||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

Initial Value | ‘0’ | ‘0’ | ‘0’ | ‘0’ | ‘0’ | ‘0’ | ‘0’ | ‘0’ | ‘0’’ | ‘0’ | ‘0’ | ‘0’ | ‘0’ | ‘0’ | ‘0’ | ‘0’ | ||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

<Description of Each Bit

BIT | Bit Name | Action | Value | Function | |

|

|

|

|

| |

|

| Read | - | Always indicate ‘0’. | |

15 - 8 | reserved |

|

|

| |

Write | - | Always write in ‘0’. | |||

|

| ||||

|

|

|

|

| |

|

| Read/ | 0 | Does not indicate ‘1’ at Port_event bit during resume processing. | |

7 | Resume_Int |

|

| ||

Write |

|

| |||

1 | Indicates ‘1’ at Port_event bit during resume processing. | ||||

|

| ||||

|

|

| |||

|

|

|

|

| |

|

|

| 0 | Does not perform short bus reset. | |

6 | ISBR | Read/ |

|

| |

|

| ||||

Write |

| Performs short bus reset. Automatically clears to ‘0’ at the completion of bus | |||

|

| 1 | |||

|

|

| reset. | ||

|

|

|

| ||

|

|

|

|

| |

|

|

| 0 | Indicates that port connection is in a loop. | |

5 | Loop | Read |

|

| |

1 | Indicates that port connection is in a loop. | ||||

| |||||

|

|

|

|

| |

|

| Write | - | Clears the bit value to ‘0’ by writing in ‘1’. | |

|

|

|

|

| |

|

|

| 0 | Indicates that the cable supply power satisfies the standard. | |

4 | Pwr_fail | Read |

|

| |

| 1 | Indicates that the cable supply power does not satisfy the standard. | |||

|

|

|

|

| |

|

| Write | - | Clears the bit value to ‘0’ by writing in ‘1’. | |

|

|

|

|

| |

|

|

| 0 | Indicates that timeout is not detected by arbitration state machine. | |

|

| Read |

|

| |

3 | Timeout |

|

|

| |

| 1 | Indicates that timeout is det ected by arbitration state machine. | |||

|

|

| |||

|

|

|

|

| |

|

| Write | - | Clears the bit value to ‘0’ by writing in ‘1’. | |

|

|

|

|

|

Rev.1.0 | 88 | Fujitsu VLSI |