LSI Specification | MB86617A |

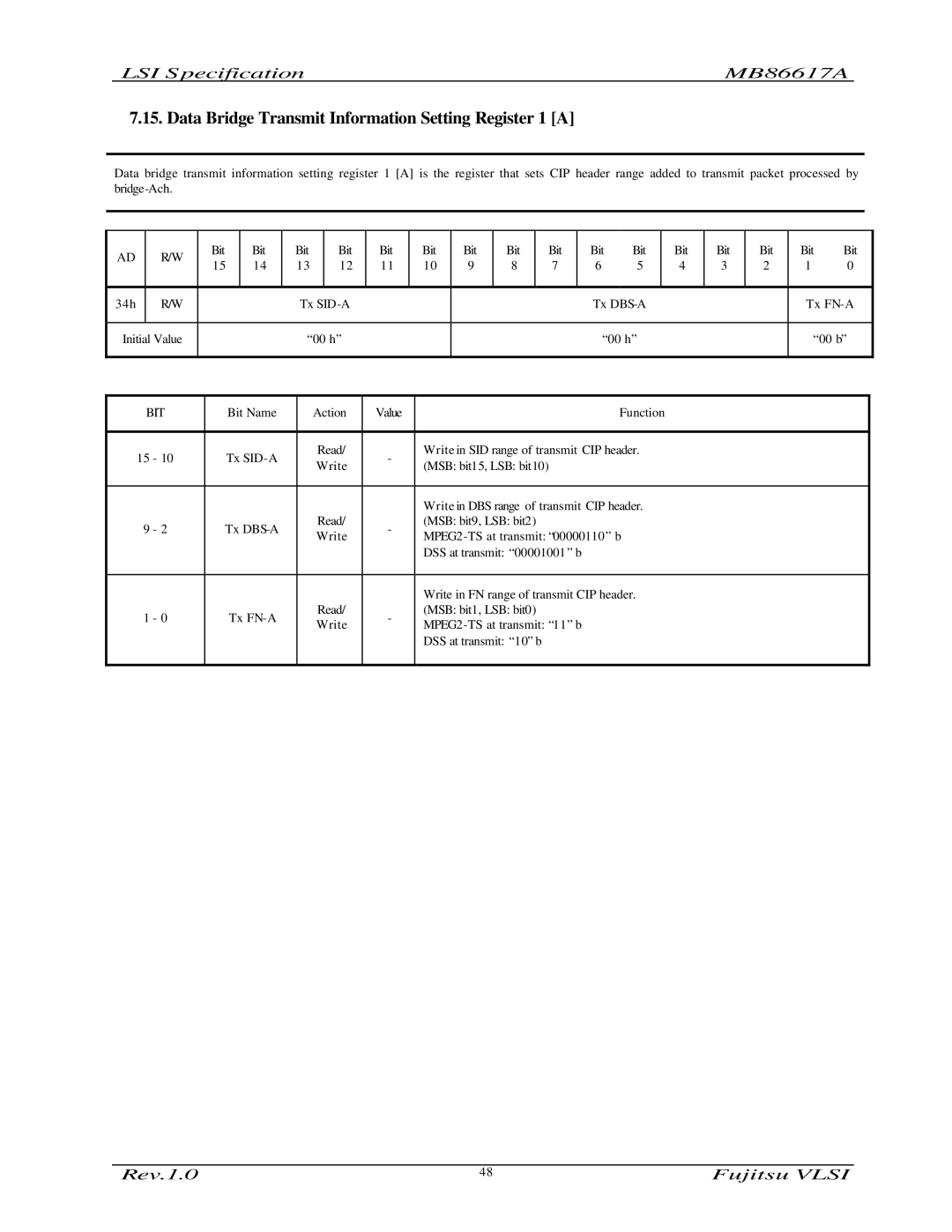

7.15. Data Bridge Transmit Information Setting Register 1 [A]

Data bridge transmit information setting register 1 [A] is the register that sets CIP header range added to transmit packet processed by

AD |

| R/W |

| Bit |

| Bit | Bit |

| Bit | Bit |

| Bit | Bit | Bit |

| Bit |

| Bit | Bit |

| Bit | Bit | Bit | Bit | Bit | ||

| 15 |

| 14 | 13 |

| 12 |

| 11 | 10 | 9 | 8 |

| 7 |

| 6 | 5 |

| 4 | 3 | 2 | 1 | 0 | |||||

|

|

|

|

|

|

|

|

| |||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||

34h |

| R/W |

|

|

|

|

| Tx |

|

|

|

|

|

|

|

| Tx |

|

|

| Tx | ||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||

Initial Value |

|

|

|

|

| “00 h” |

|

|

|

|

|

|

|

| “00 h” |

|

|

| “00 b” | ||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||

|

| BIT |

|

| Bit Name |

|

| Action |

| Value |

|

|

|

|

|

|

|

| Function |

|

|

|

|

| |||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||

| 15 - 10 |

|

| Tx |

|

| Read/ |

| - |

| Write in SID range of transmit CIP header. |

|

|

|

|

| |||||||||||

|

|

|

|

| Write |

|

| (MSB: bit15, LSB: bit10) |

|

|

|

|

|

|

|

| |||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

| Write in DBS range of transmit CIP header. |

|

|

|

|

| ||||||||

| 9 - 2 |

|

| Tx |

|

| Read/ |

| - |

| (MSB: bit9, LSB: bit2) |

|

|

|

|

|

|

|

|

|

| ||||||

|

|

|

|

| Write |

|

|

|

|

|

|

| |||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

| DSS at transmit: “00001001” b |

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

| Write in FN range of transmit CIP header. |

|

|

|

|

| ||||||||

| 1 - 0 |

|

| Tx |

|

| Read/ |

| - |

| (MSB: bit1, LSB: bit0) |

|

|

|

|

|

|

|

|

|

| ||||||

|

|

|

|

| Write |

|

|

|

|

|

|

|

|

|

| ||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

| DSS at transmit: “10” b |

|

|

|

|

|

|

|

|

|

| |||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Rev.1.0 | 48 | Fujitsu VLSI |