LSI Specification | MB86617A |

11.1. Initialization

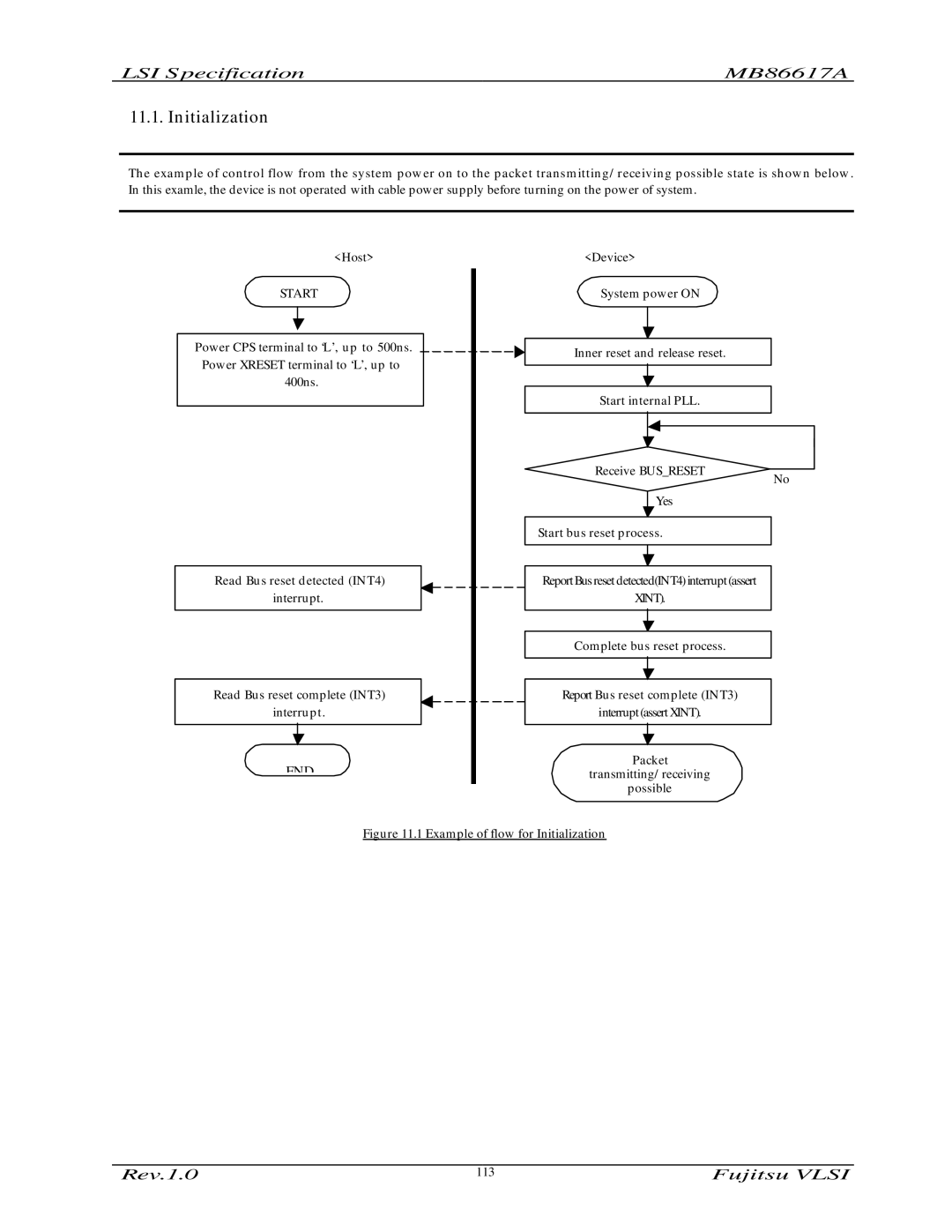

The example of control flow from the system power on to the packet transmitting/receiving possible state is shown below. In this examle, the device is not operated with cable power supply before turning on the power of system.

<Host>

START

Power CPS terminal to ‘L’, up to 500ns. Power XRESET terminal to ‘L’, up to 400ns.

Read Bus reset detected (INT4) interrupt.

Read Bus reset complete (INT3)

interrupt.

END

<Device>

System power ON

Inner reset and release reset.

Start internal PLL.

Receive BUS_RESET | No |

|

Yes

Start bus reset process.

ReportBusresetdetected(INT4)interrupt(assert

XINT).

Complete bus reset process.

Report Bus reset complete (INT3)

interrupt(assertXINT).

Packet

transmitting/receiving

possible

Figure 11.1 Example of flow for Initialization

Rev.1.0 | 113 | Fujitsu VLSI |