| LSI Specification |

|

|

|

|

|

|

|

|

|

| MB86617A |

| |||||||

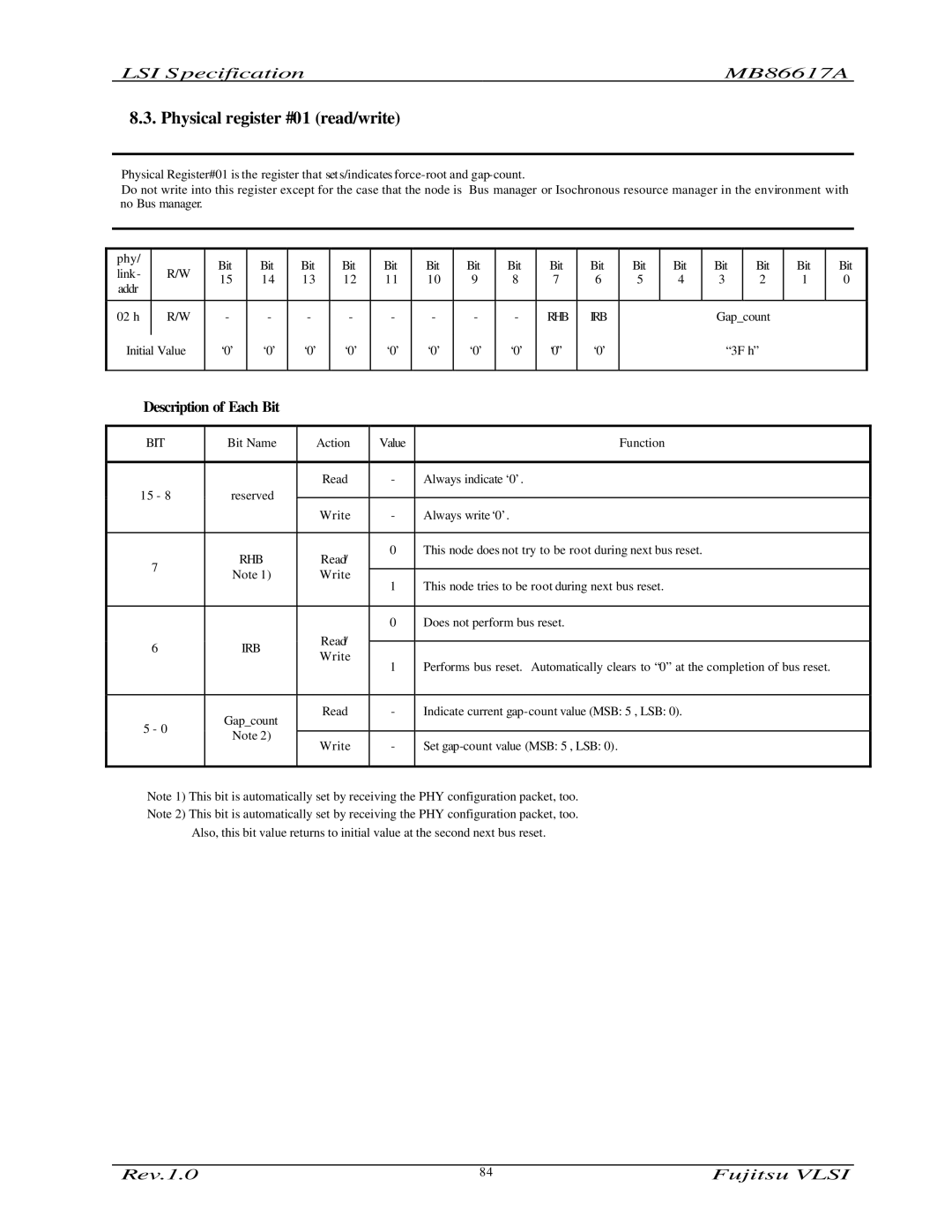

| 8.3. Physical register #01 (read/write) |

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

| Physical Register#01 is the register that set s/indicates |

|

|

|

|

|

|

|

|

| ||||||||||

| Do not write into this register except for the case that the node is | Bus manager or Isochronous resource manager in the environment with |

| |||||||||||||||||

| no Bus manager. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| phy/ |

| Bit | Bit | Bit | Bit | Bit | Bit |

| Bit | Bit | Bit | Bit | Bit | Bit | Bit | Bit | Bit | Bit |

|

| link- | R/W |

|

| ||||||||||||||||

| 15 | 14 | 13 | 12 | 11 | 10 |

| 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| ||

| addr |

|

|

| ||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 02 h | R/W | - | - | - | - | - | - |

| - | - | RHB | IRB |

|

| Gap_count |

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

| Initial Value | ‘0’ | ‘0’ | ‘0’ | ‘0’ | ‘0’ | ‘0’ |

| ‘0’ | ‘0’ | ‘0’’ | ‘0’ |

|

| “3F h” |

|

|

| ||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ョDescription of Each Bit

BIT | Bit Name | Action | Value | Function | |

|

|

|

|

| |

|

| Read | - | Always indicate ‘0’. | |

15 - 8 | reserved |

|

|

| |

Write | - | Always write‘0’. | |||

|

| ||||

|

|

|

|

| |

| RHB | Read/ | 0 | This node does not try to be root during next bus reset. | |

7 |

|

| |||

Note 1) | Write | 1 | This node tries to be root during next bus reset. | ||

| |||||

|

|

| |||

|

|

|

|

| |

|

|

| 0 | Does not perform bus reset. | |

6 | IRB | Read/ |

|

| |

|

| ||||

Write |

|

| |||

|

| 1 | Performs bus reset. Automatically clears to “0” at the completion of bus reset. | ||

|

|

| |||

|

|

|

|

| |

| Gap_count | Read | - | Indicate current | |

5 - 0 |

|

|

| ||

Note 2) |

|

|

| ||

Write | - | Set | |||

| |||||

|

| ||||

|

|

|

|

|

Note 1) This bit is automatically set by receiving the PHY configuration packet, too.

Note 2) This bit is automatically set by receiving the PHY configuration packet, too.

Also, this bit value returns to initial value at the second next bus reset.

Rev.1.0 | 84 | Fujitsu VLSI |