| LSI Specification |

|

|

| MB86617A | |||

|

|

|

|

|

|

|

|

|

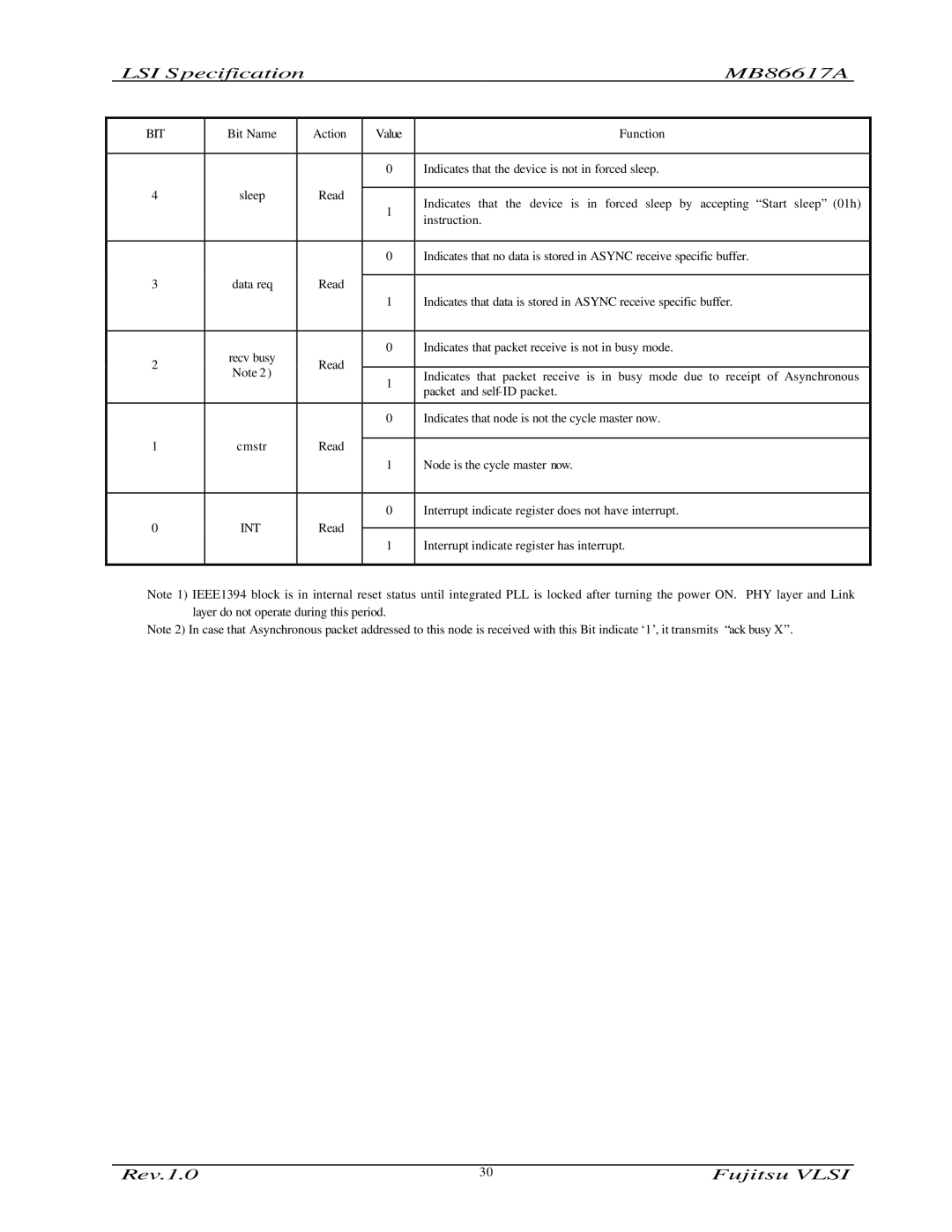

| BIT | Bit Name |

| Action | Value | Function |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 0 | Indicates that the device is not in forced sleep. |

|

|

| 4 | sleep |

| Read |

|

|

|

|

|

| 1 | Indicates that the device is in forced sleep | by accepting “Start sleep” (01h) | ||||

|

|

|

|

| ||||

|

|

|

|

| instruction. |

|

| |

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

| ||

|

|

|

|

| 0 | Indicates that no data is stored in ASYNC receive specific buffer. | ||

| 3 | data req |

| Read |

|

|

|

|

|

|

|

|

|

| |||

|

|

|

|

| 1 | Indicates that data is stored in ASYNC receive specific buffer. | ||

|

|

|

|

|

|

|

|

|

|

| recv busy |

|

| 0 | Indicates that packet receive is not in busy mode. |

|

|

| 2 |

| Read |

|

|

|

| |

| Note 2) |

| 1 | Indicates that packet receive is in busy mode | due to receipt of Asynchronous | |||

|

|

|

| |||||

|

|

|

|

| packet and |

|

| |

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

| 0 | Indicates that node is not the cycle master now. |

|

|

| 1 | cmstr |

| Read |

|

|

|

|

|

| 1 | Node is the cycle master now. |

|

| |||

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

|

|

|

|

|

|

| 0 | Interrupt indicate register does not have interrupt. |

|

|

| 0 | INT |

| Read |

|

|

|

|

| 1 | Interrupt indicate register has interrupt. |

|

| ||||

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

|

|

Note 1) IEEE1394 block is in internal reset status until integrated PLL is locked after turning the power ON. PHY layer and Link layer do not operate during this period.

Note 2) In case that Asynchronous packet addressed to this node is received with this Bit indicate ‘1’, it transmits “ack busy X”.

Rev.1.0 | 30 | Fujitsu VLSI |