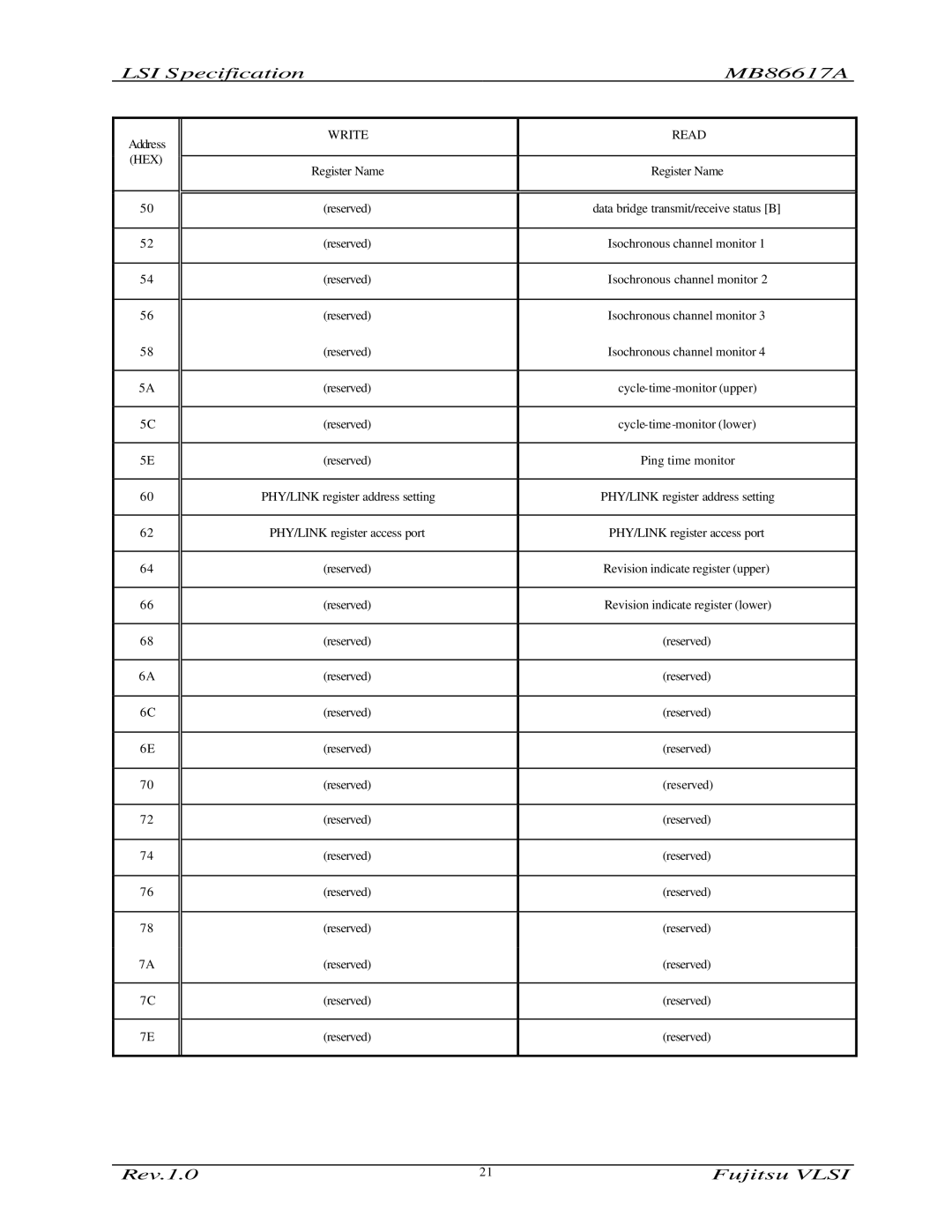

LSI Specification | MB86617A |

Address (HEX)

50

52

54

56

58

5A

5C

5E

60

62

64

66

68

6A

6C

6E

70

72

74

76

78

7A

7C

7E

WRITE | READ |

|

|

Register Name | Register Name |

|

|

|

|

(reserved) | data bridge transmit/receive status [B] |

|

|

(reserved) | Isochronous channel monitor 1 |

|

|

(reserved) | Isochronous channel monitor 2 |

|

|

(reserved) | Isochronous channel monitor 3 |

(reserved) | Isochronous channel monitor 4 |

|

|

(reserved) | |

|

|

(reserved) | |

|

|

(reserved) | Ping time monitor |

|

|

PHY/LINK register address setting | PHY/LINK register address setting |

|

|

PHY/LINK register access port | PHY/LINK register access port |

|

|

(reserved) | Revision indicate register (upper) |

|

|

(reserved) | Revision indicate register (lower) |

|

|

(reserved) | (reserved) |

|

|

(reserved) | (reserved) |

|

|

(reserved) | (reserved) |

|

|

(reserved) | (reserved) |

|

|

(reserved) | (reserved) |

|

|

(reserved) | (reserved) |

|

|

(reserved) | (reserved) |

|

|

(reserved) | (reserved) |

|

|

(reserved) | (reserved) |

(reserved) | (reserved) |

|

|

(reserved) | (reserved) |

|

|

(reserved) | (reserved) |

|

|

Rev.1.0 | 21 | Fujitsu VLSI |