LSI Specification | MB86617A |

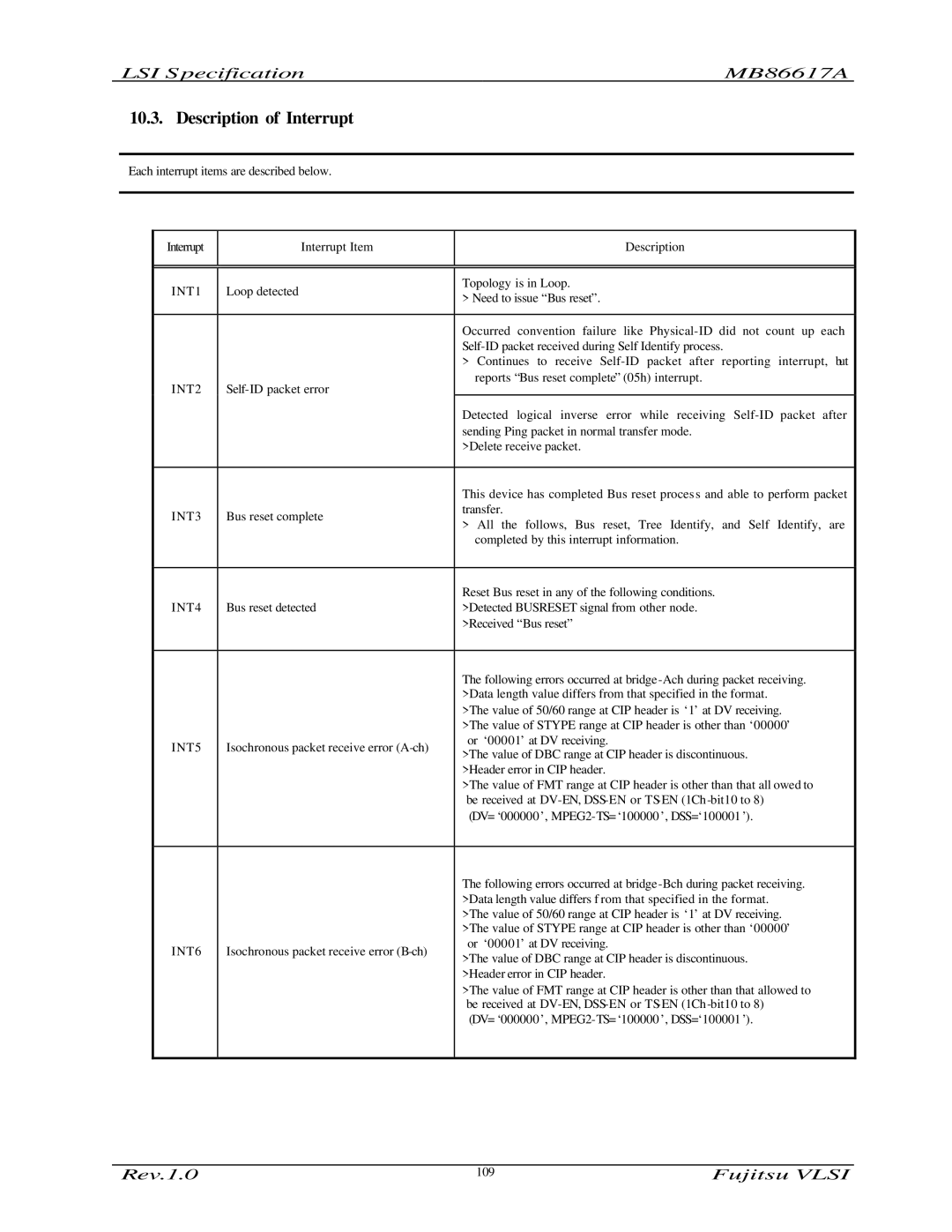

10.3. Description of Interrupt

Each interrupt items are described below.

Interrupt | Interrupt Item | Description | |

|

|

| |

|

|

| |

INT1 | Loop detected | Topology is in Loop. | |

> Need to issue “Bus reset”. | |||

|

| ||

|

|

| |

|

| Occurred convention failure like | |

|

| ||

|

| > Continues to receive | |

INT2 | reports “Bus reset complete” (05h) interrupt. | ||

| |||

|

| Detected logical inverse error while receiving | |

|

| sending Ping packet in normal transfer mode. | |

|

| >Delete receive packet. | |

|

|

| |

|

| This device has completed Bus reset process and able to perform packet | |

INT3 | Bus reset complete | transfer. | |

> All the follows, Bus reset, Tree Identify, and Self Identify, are | |||

|

| ||

|

| completed by this interrupt information. | |

|

|

| |

|

| Reset Bus reset in any of the following conditions. | |

INT4 | Bus reset detected | >Detected BUSRESET signal from other node. | |

|

| >Received “Bus reset” | |

|

|

| |

|

| The following errors occurred at | |

|

| >Data length value differs from that specified in the format. | |

|

| >The value of 50/60 range at CIP header is ‘1’ at DV receiving. | |

|

| >The value of STYPE range at CIP header is other than ‘00000’ | |

INT5 | Isochronous packet receive error | or ‘00001’ at DV receiving. | |

>The value of DBC range at CIP header is discontinuous. | |||

|

| ||

|

| >Header error in CIP header. | |

|

| >The value of FMT range at CIP header is other than that all owed to | |

|

| be received at | |

|

| (DV= ‘000000’, | |

|

|

| |

|

| The following errors occurred at | |

|

| >Data length value differs f rom that specified in the format. | |

|

| >The value of 50/60 range at CIP header is ‘1’ at DV receiving. | |

|

| >The value of STYPE range at CIP header is other than ‘00000’ | |

INT6 | Isochronous packet receive error | or ‘00001’ at DV receiving. | |

>The value of DBC range at CIP header is discontinuous. | |||

|

| ||

|

| >Header error in CIP header. | |

|

| >The value of FMT range at CIP header is other than that allowed to | |

|

| be received at | |

|

| (DV= ‘000000’, | |

|

|

|

Rev.1.0 | 109 | Fujitsu VLSI |