LSI Specification | MB86617A |

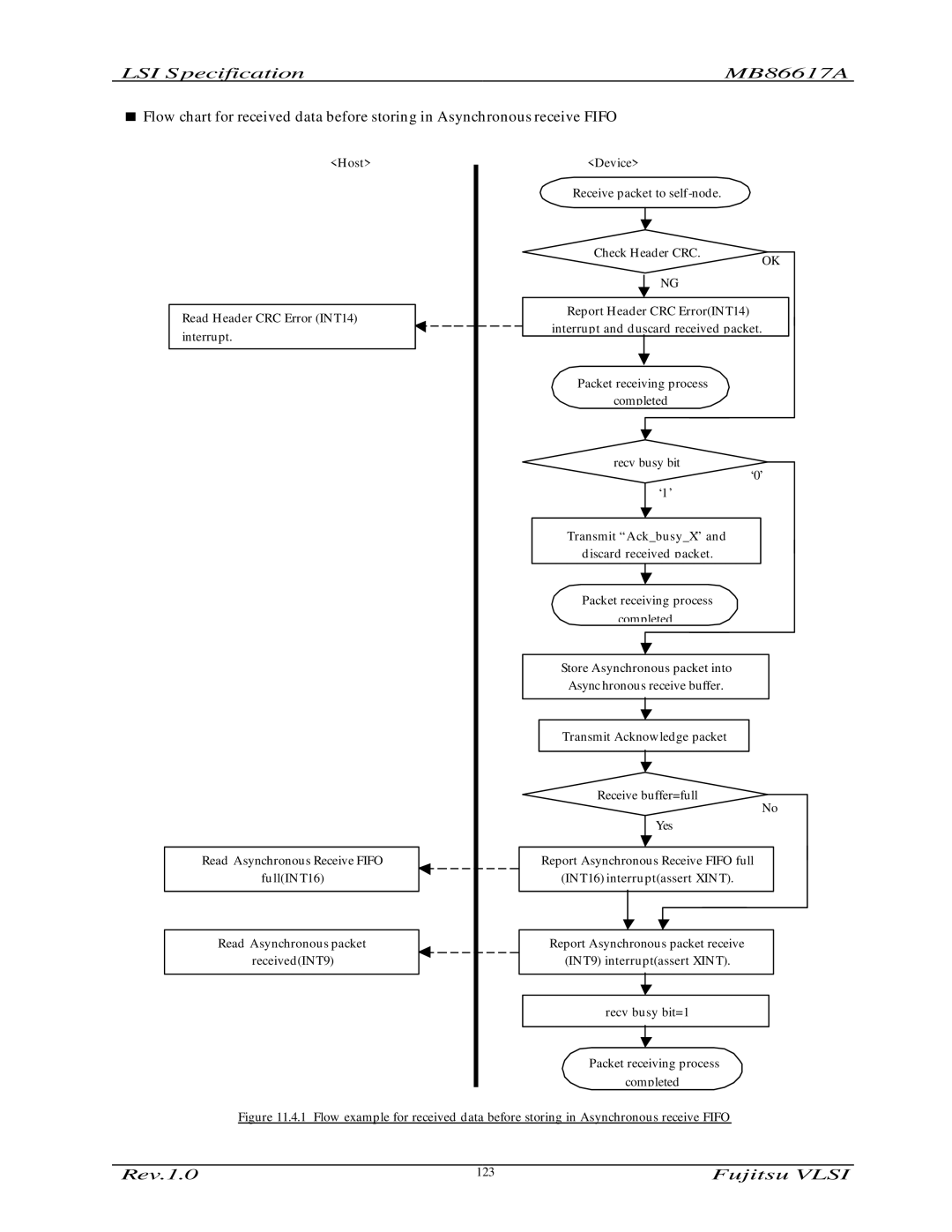

<Flow chart for received data before storing in Asynchronous receive FIFO

<Host>

Read Header CRC Error (INT14) interrupt.

Read Asynchronous Receive FIFO

full(INT16)

Read Asynchronous packet

received(INT9)

<Device>

Receive packet to

Check Header CRC. | OK |

| |

NG |

|

Report Header CRC Error(INT14) |

|

interrupt and duscard received packet. | |

Packet receiving process |

|

completed |

|

recv busy bit |

‘0’ |

‘1’ |

Transmit “Ack_busy_X” and |

discard received packet. |

Packet receiving process |

completed |

Store Asynchronous packet into

Async hronous receive buffer.

Transmit Acknowledge packet

Receive buffer=full

No

Yes

Report Asynchronous Receive FIFO full

(INT16) interrupt(assert XINT).

Report Asynchronous packet receive

(INT9) interrupt(assert XINT).

recv busy bit=1

Packet receiving process completed

Figure 11.4.1 Flow example for received data before storing in Asynchronous receive FIFO

Rev.1.0 | 123 | Fujitsu VLSI |