| LSI Specification |

|

| MB86617A |

| ||

|

|

|

|

|

|

| |

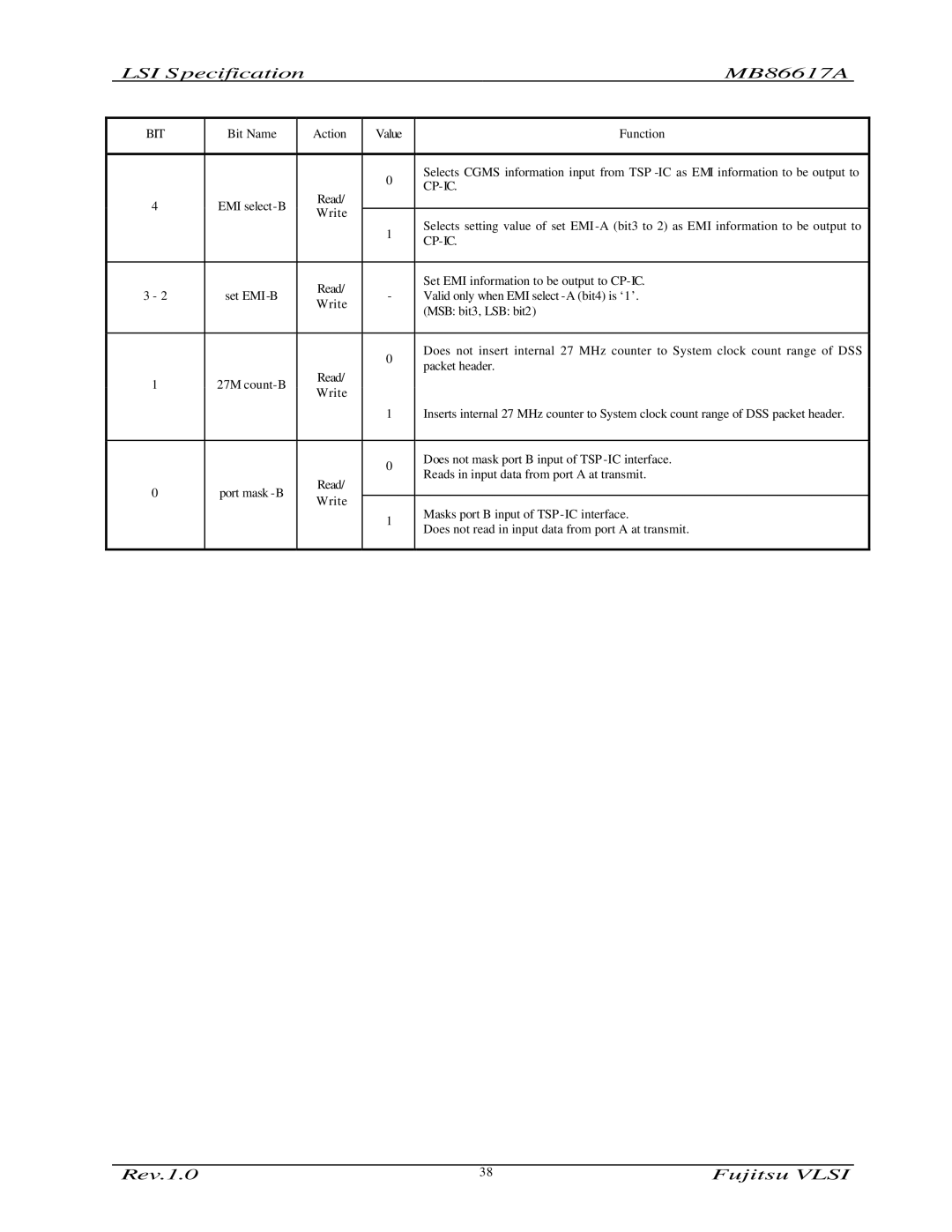

| BIT | Bit Name |

| Action | Value | Function | |

|

|

|

|

|

|

| |

|

|

|

|

| 0 | Selects CGMS information input from TSP | |

|

|

|

|

|

| ||

|

|

|

| Read/ |

| ||

| 4 | EMI |

|

|

|

| |

|

| Write |

| Selects setting value of set EMI | |||

|

|

|

|

| |||

|

|

|

|

| 1 | ||

|

|

|

|

|

| ||

|

|

|

|

|

| ||

|

|

|

|

|

|

| |

|

|

|

| Read/ |

| Set EMI information to be output to | |

| 3 - 2 | set |

| - | Valid only when EMI select | ||

|

| Write | |||||

|

|

|

|

| (MSB: bit3, LSB: bit2) | ||

|

|

|

|

|

| ||

|

|

|

|

|

|

| |

|

|

|

|

| 0 | Does not insert internal 27 MHz counter to System clock count range of DSS | |

|

|

|

|

| packet header. | ||

|

|

|

| Read/ |

| ||

| 1 | 27M |

|

|

|

| |

|

| Write |

|

|

| ||

|

|

|

|

|

|

| |

|

|

|

|

| 1 | Inserts internal 27 MHz counter to System clock count range of DSS packet header. | |

|

|

|

|

|

|

| |

|

|

|

|

| 0 | Does not mask port B input of TSP | |

|

|

|

|

| Reads in input data from port A at transmit. | ||

|

|

|

| Read/ |

| ||

| 0 | port mask |

|

|

|

| |

|

| Write |

|

|

| ||

|

| Masks port B input of TSP | |||||

|

|

|

|

| |||

|

|

|

|

| 1 | ||

|

|

|

|

| Does not read in input data from port A at transmit. | ||

|

|

|

|

|

| ||

|

|

|

|

|

|

|

|

Rev.1.0 | 38 | Fujitsu VLSI |