LSI Specification | MB86617A |

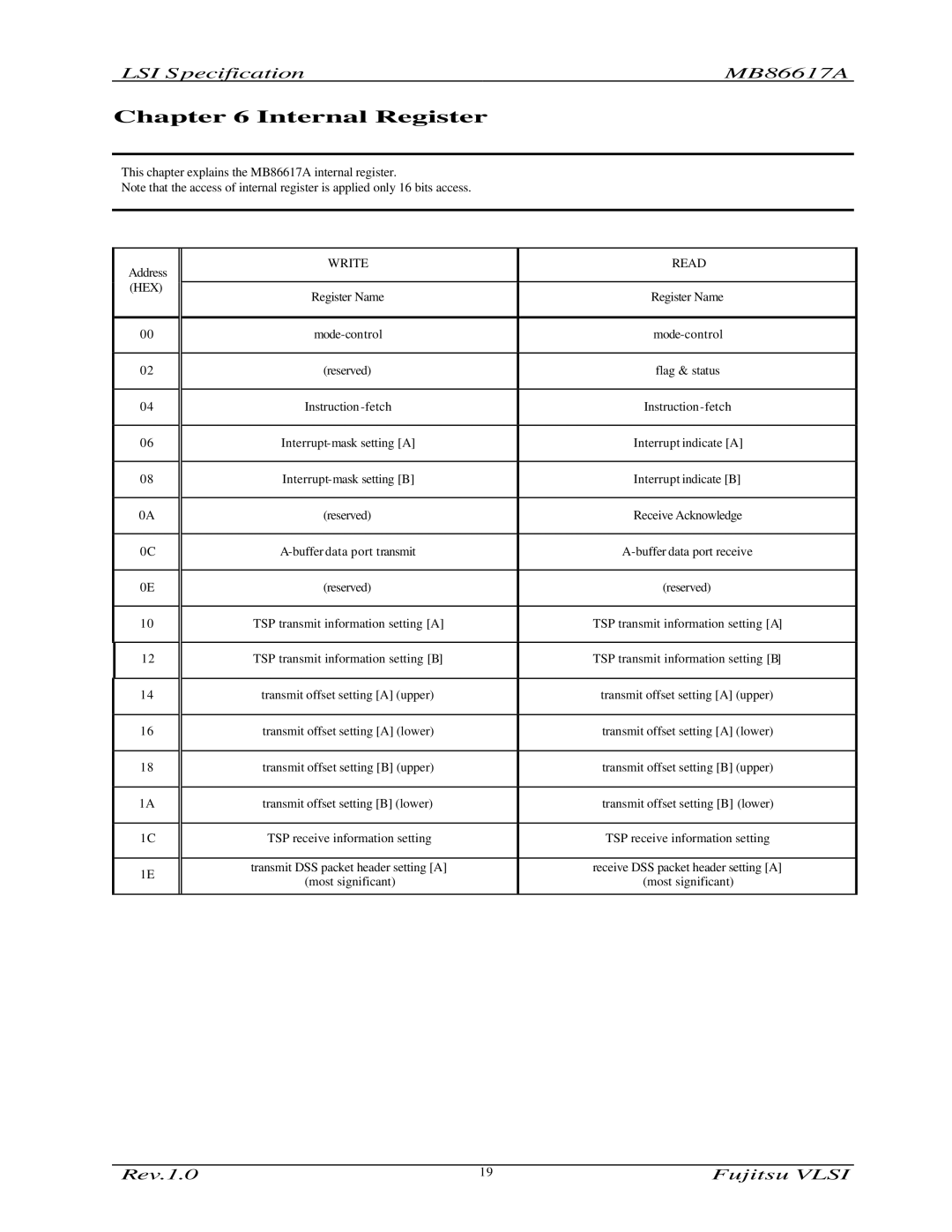

Chapter 6 Internal Register

This chapter explains the MB86617A internal register.

Note that the access of internal register is applied only 16 bits access.

Address (HEX)

00

02

04

06

08

0A

0C

0E

10

12

14

16

18

1A

1C

1E

WRITE | READ |

|

|

Register Name | Register Name |

|

|

|

|

(reserved) | flag & status |

|

|

Instruction | Instruction |

|

|

Interrupt indicate [A] | |

|

|

Interrupt indicate [B] | |

|

|

(reserved) | Receive Acknowledge |

|

|

|

|

(reserved) | (reserved) |

|

|

TSP transmit information setting [A] | TSP transmit information setting [A] |

|

|

TSP transmit information setting [B] | TSP transmit information setting [B] |

|

|

transmit offset setting [A] (upper) | transmit offset setting [A] (upper) |

|

|

transmit offset setting [A] (lower) | transmit offset setting [A] (lower) |

|

|

transmit offset setting [B] (upper) | transmit offset setting [B] (upper) |

|

|

transmit offset setting [B] (lower) | transmit offset setting [B] (lower) |

|

|

TSP receive information setting | TSP receive information setting |

|

|

transmit DSS packet header setting [A] | receive DSS packet header setting [A] |

(most significant) | (most significant) |

|

|

Rev.1.0 | 19 | Fujitsu VLSI |