LSI Specification | MB86617A |

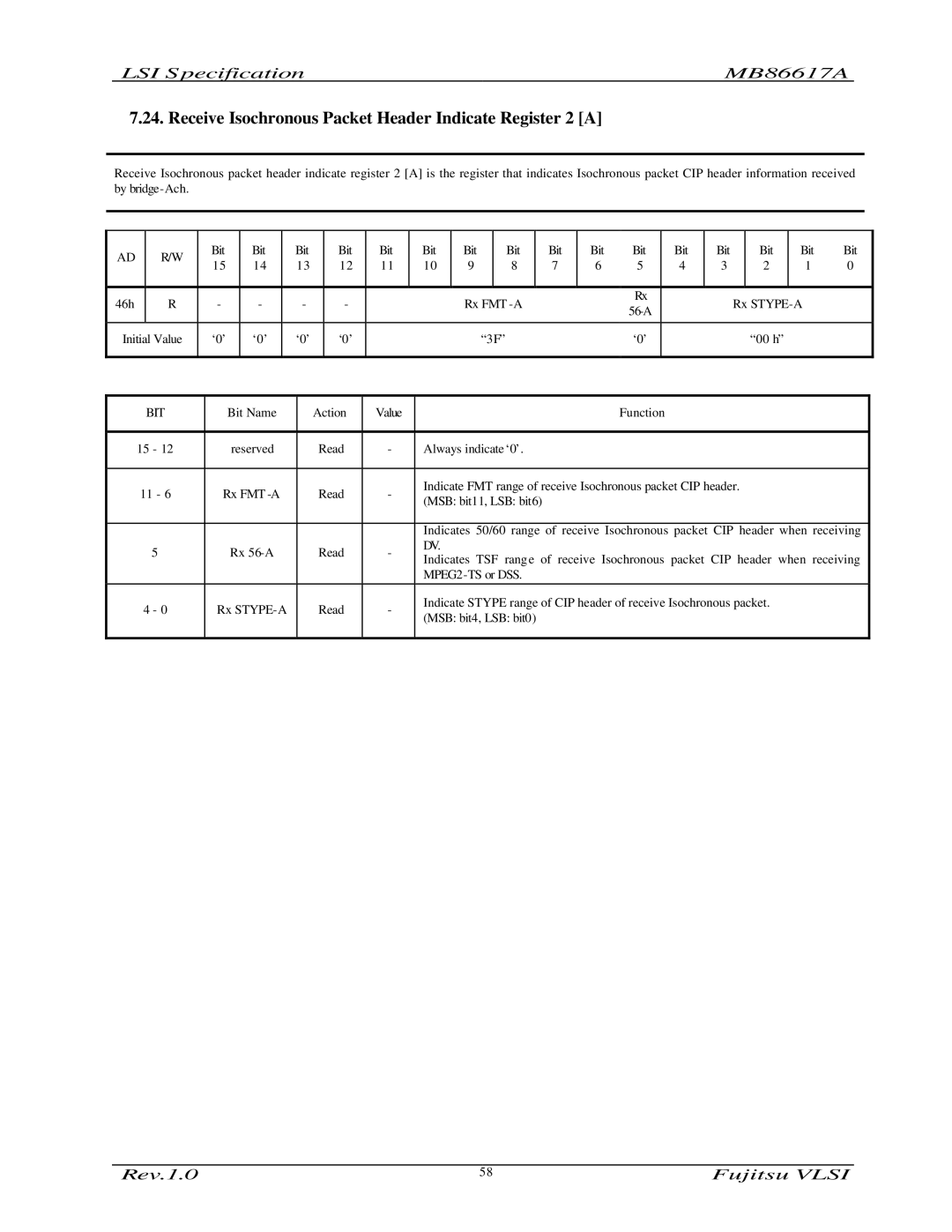

7.24. Receive Isochronous Packet Header Indicate Register 2 [A]

Receive Isochronous packet header indicate register 2 [A] is the register that indicates Isochronous packet CIP header information received by

AD |

| R/W |

| Bit |

| Bit |

| Bit |

| Bit | Bit |

| Bit | Bit |

| Bit |

| Bit | Bit | Bit |

| Bit | Bit | Bit | Bit | Bit | |||

| 15 |

| 14 |

| 13 |

| 12 |

| 11 | 10 | 9 |

| 8 |

| 7 | 6 | 5 |

| 4 | 3 | 2 | 1 | 0 |

| |||||

|

|

|

|

|

|

|

|

|

|

| |||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

46h |

| R | - |

| - |

| - |

| - |

|

|

|

| Rx FMT |

|

| Rx |

|

| Rx |

|

| |||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||

Initial Value |

| ‘0’ |

| ‘0’ |

| ‘0’ |

| ‘0’ |

|

|

|

| “3F” |

|

| ‘0’ |

|

|

| “00 h” |

|

|

| ||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||

|

| BIT |

|

| Bit Name |

|

| Action |

| Value |

|

|

|

|

|

|

|

| Function |

|

|

|

|

|

| ||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||

| 15 - 12 |

|

| reserved |

|

| Read |

| - |

| Always indicate‘0’. |

|

|

|

|

|

|

|

|

|

| ||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||||

| 11 - 6 |

| Rx FMT |

|

| Read |

| - |

| Indicate FMT range of receive Isochronous packet CIP header. |

|

|

|

| |||||||||||||||

|

|

|

|

|

| (MSB: bit11, LSB: bit6) |

|

|

|

|

|

|

|

|

|

| |||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| Indicates 50/60 range of receive Isochronous packet CIP header when receiving | ||||||||||||||

| 5 |

|

| Rx |

|

| Read |

| - |

| DV. |

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||

|

|

|

|

|

|

| Indicates TSF range of receive Isochronous packet CIP header when receiving |

| |||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||

| 4 - 0 |

| Rx |

|

| Read |

| - |

| Indicate STYPE range of CIP header of receive Isochronous packet. |

|

|

| ||||||||||||||||

|

|

|

|

|

| (MSB: bit4, LSB: bit0) |

|

|

|

|

|

|

|

|

|

| |||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Rev.1.0 | 58 | Fujitsu VLSI |