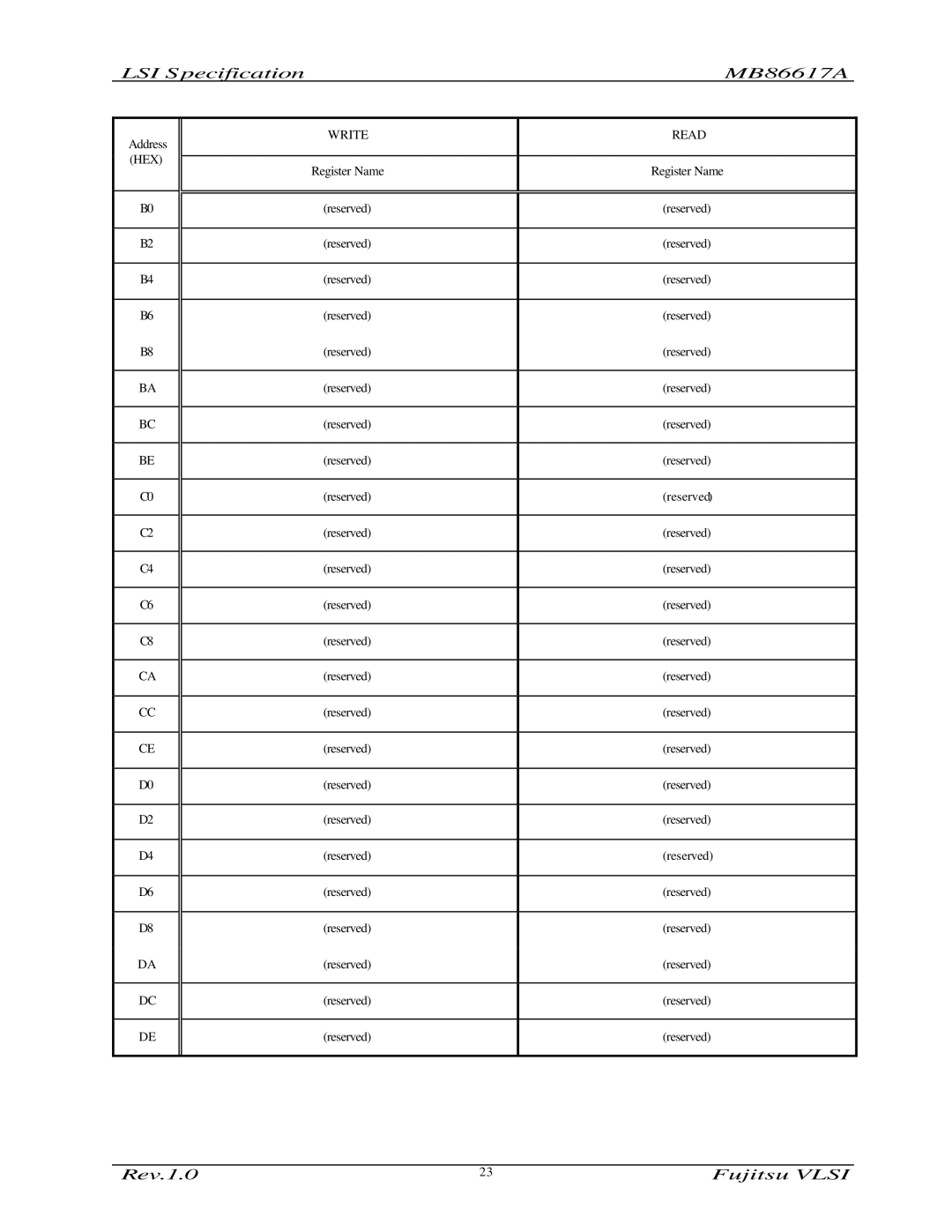

LSI Specification | MB86617A |

Address (HEX)

B0

B2

B4

B6

B8

BA

BC

BE

C0

C2

C4

C6

C8

CA

CC

CE

D0

D2

D4

D6

D8

DA

DC

DE

WRITE | READ |

|

|

Register Name | Register Name |

|

|

|

|

(reserved) | (reserved) |

|

|

(reserved) | (reserved) |

|

|

(reserved) | (reserved) |

|

|

(reserved) | (reserved) |

(reserved) | (reserved) |

|

|

(reserved) | (reserved) |

|

|

(reserved) | (reserved) |

|

|

(reserved) | (reserved) |

|

|

(reserved) | (reserved) |

|

|

(reserved) | (reserved) |

|

|

(reserved) | (reserved) |

|

|

(reserved) | (reserved) |

|

|

(reserved) | (reserved) |

|

|

(reserved) | (reserved) |

|

|

(reserved) | (reserved) |

|

|

(reserved) | (reserved) |

|

|

(reserved) | (reserved) |

|

|

(reserved) | (reserved) |

|

|

(reserved) | (reserved) |

|

|

(reserved) | (reserved) |

|

|

(reserved) | (reserved) |

(reserved) | (reserved) |

|

|

(reserved) | (reserved) |

|

|

(reserved) | (reserved) |

|

|

Rev.1.0 | 23 | Fujitsu VLSI |