LSI Specification | MB86617A |

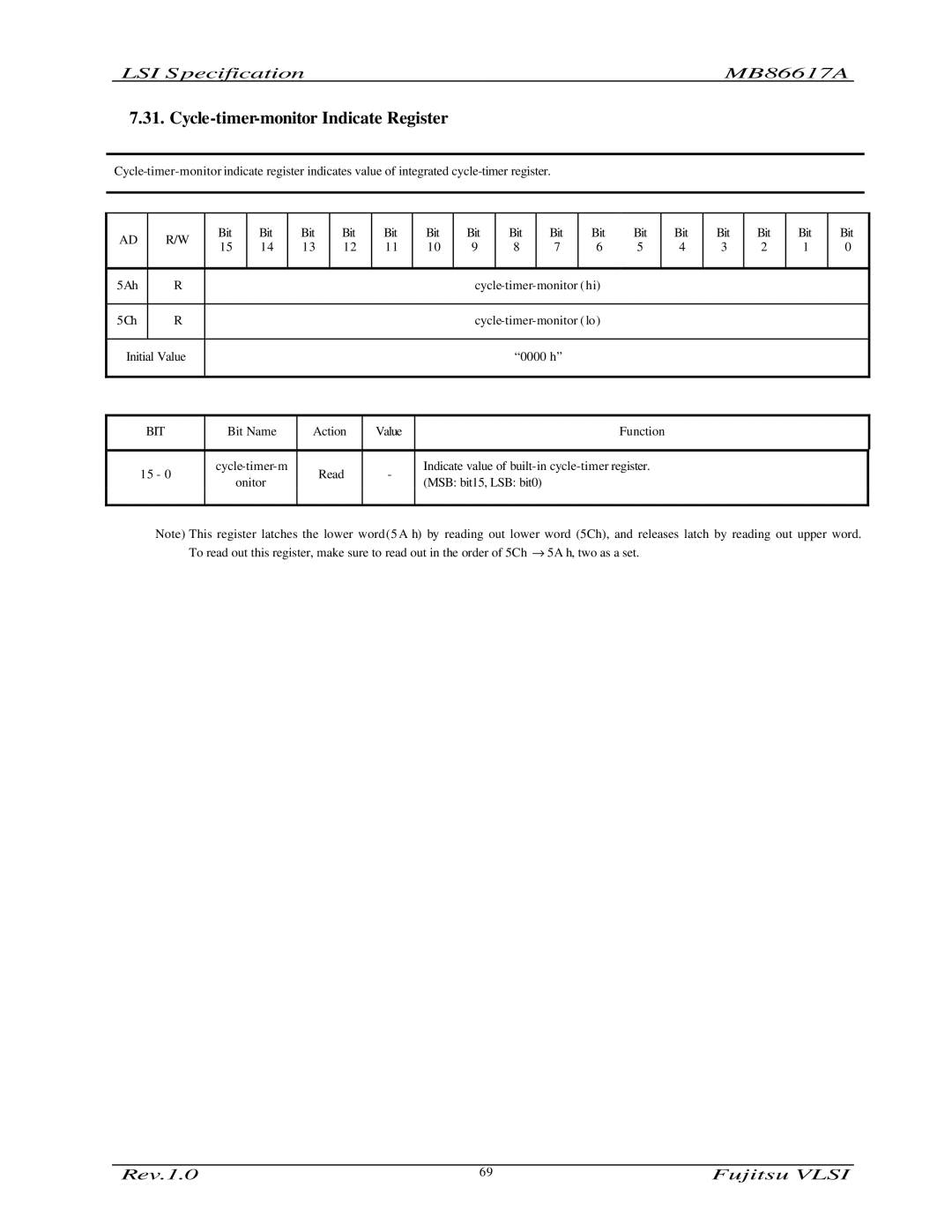

7.31. Cycle-timer-monitor Indicate Register

AD |

| R/W | Bit |

| Bit |

| Bit |

| Bit | Bit | Bit | Bit | Bit |

| Bit | Bit | Bit |

| Bit | Bit | Bit | Bit | Bit | |

| 15 |

| 14 | 13 |

| 12 |

| 11 | 10 | 9 | 8 |

| 7 | 6 | 5 |

| 4 | 3 | 2 | 1 | 0 | |||

|

|

|

|

|

|

|

| |||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

5Ah |

| R |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||

5Ch |

| R |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||

Initial Value |

|

|

|

|

|

|

|

|

|

|

| “0000 h” |

|

|

|

|

|

|

|

| ||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||

BIT |

| Bit Name |

| Action |

| Value |

|

|

|

|

|

| Function |

|

|

|

|

| ||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||

15 - 0 |

|

| Read |

| - | Indicate value of |

|

|

|

|

| |||||||||||||

| onitor |

|

|

| (MSB: bit15, LSB: bit0) |

|

|

|

|

|

|

|

|

| ||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Note) This register latches the lower word (5 A h) by reading out lower word (5Ch), and releases latch by reading out upper word. To read out this register, make sure to read out in the order of 5Ch → 5A h, two as a set.

Rev.1.0 | 69 | Fujitsu VLSI |