LSI Specification |

| MB86617A | |||

|

|

|

|

|

|

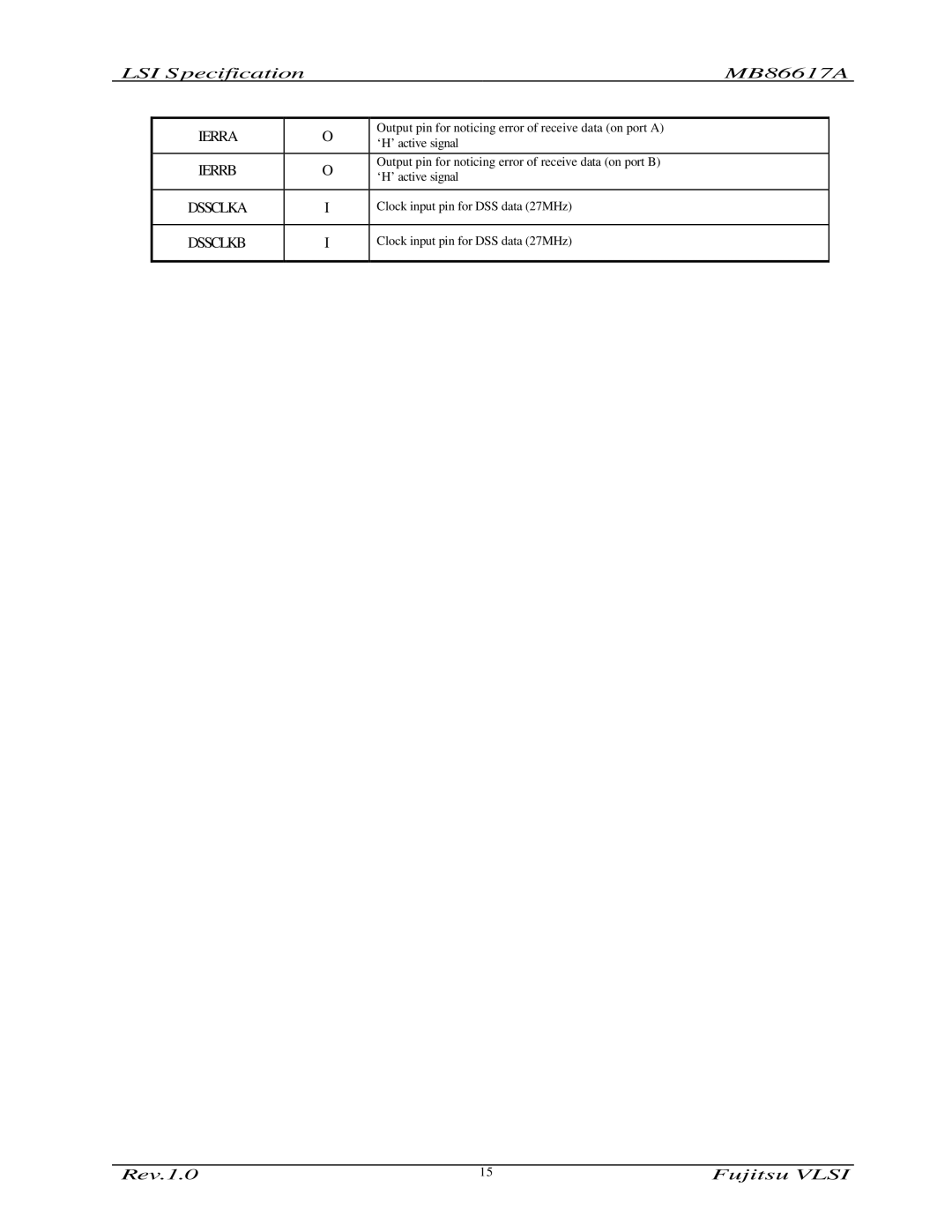

| IERRA |

| O | Output pin for noticing error of receive data (on port A) |

|

|

| ‘H’ active signal |

| ||

|

|

|

|

| |

|

|

|

|

|

|

| IERRB |

| O | Output pin for noticing error of receive data (on port B) |

|

|

| ‘H’ active signal |

| ||

|

|

|

|

| |

|

|

|

|

|

|

| DSSCLKA |

| I | Clock input pin for DSS data (27MHz) |

|

|

|

|

|

|

|

| DSSCLKB |

| I | Clock input pin for DSS data (27MHz) |

|

|

|

|

|

|

|

Rev.1.0 | 15 | Fujitsu VLSI |