LSI Specification | MB86617A | ||

|

|

|

|

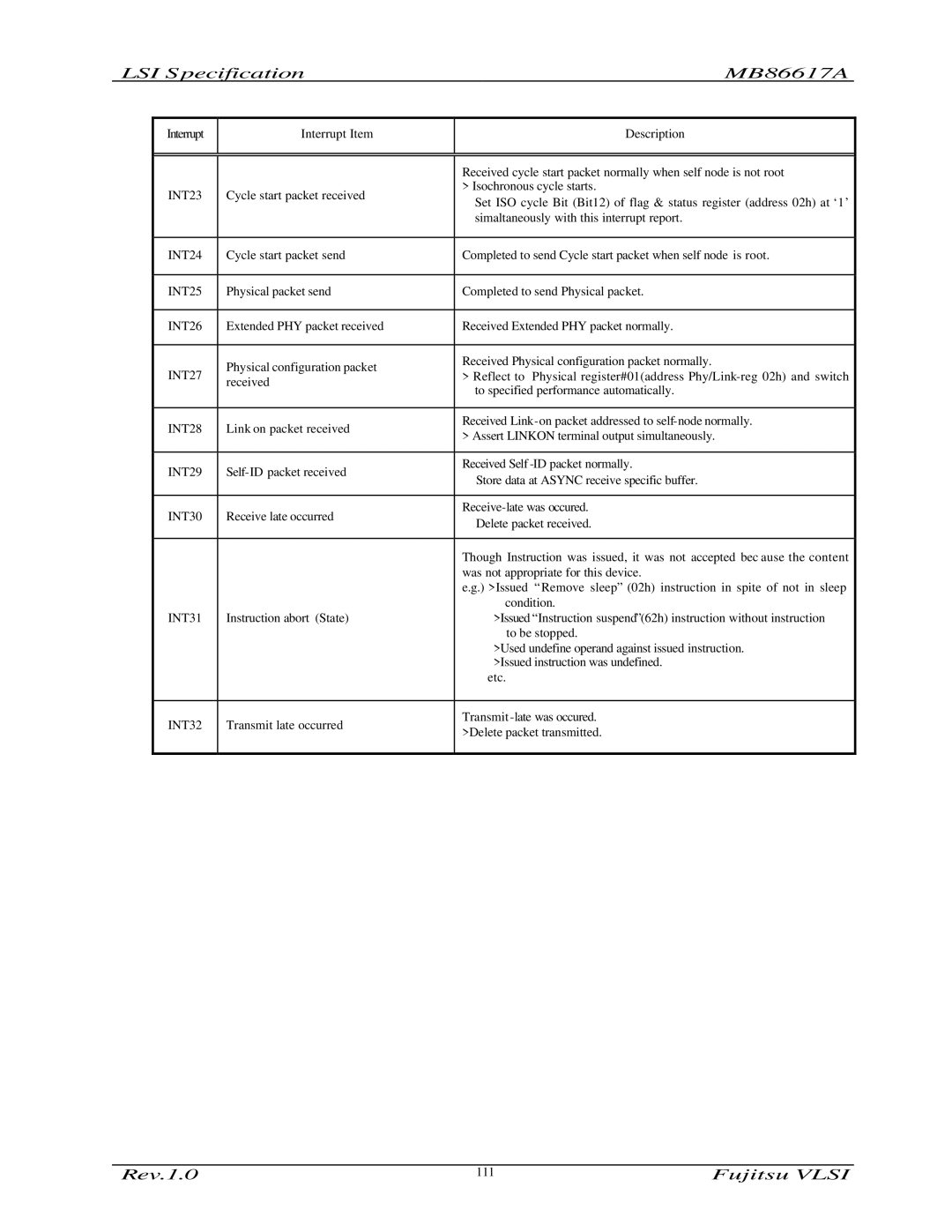

| Interrupt | Interrupt Item | Description |

|

|

|

|

|

|

|

|

|

|

| Received cycle start packet normally when self node is not root |

| INT23 | Cycle start packet received | > Isochronous cycle starts. |

| Set ISO cycle Bit (Bit12) of flag & status register (address 02h) at ‘1’ | ||

|

|

| |

|

|

| simaltaneously with this interrupt report. |

|

|

|

|

| INT24 | Cycle start packet send | Completed to send Cycle start packet when self node is root. |

|

|

|

|

| INT25 | Physical packet send | Completed to send Physical packet. |

|

|

|

|

| INT26 | Extended PHY packet received | Received Extended PHY packet normally. |

|

|

|

|

| INT27 | Physical configuration packet | Received Physical configuration packet normally. |

| > Reflect to Physical register#01(address | ||

| received | ||

|

| to specified performance automatically. | |

|

|

| |

|

|

|

|

| INT28 | Link on packet received | Received |

| > Assert LINKON terminal output simultaneously. | ||

|

|

| |

|

|

|

|

| INT29 | Received Self | |

| ョStore data at ASYNC receive specific buffer. | ||

|

|

| |

|

|

|

|

| INT30 | Receive late occurred | |

| ョDelete packet received. | ||

|

|

| |

|

|

|

|

|

|

| Though Instruction was issued, it was not accepted bec ause the content |

|

|

| was not appropriate for this device. |

|

|

| e.g.) >Issued “ Remove sleep” (02h) instruction in spite of not in sleep |

|

|

| condition. |

| INT31 | Instruction abort (State) | >Issued “Instruction suspend”(62h) instruction without instruction |

|

|

| to be stopped. |

|

|

| >Used undefine operand against issued instruction. |

|

|

| >Issued instruction was undefined. |

|

|

| etc. |

|

|

|

|

| INT32 | Transmit late occurred | Transmit |

| >Delete packet transmitted. | ||

|

|

| |

|

|

|

|

Rev.1.0 | 111 | Fujitsu VLSI |