Contents

LSI Specification MB86617A

Contents

Rev.1.0

101

106

Overview

Features

Chapte r 3 Chip Block

TPA1

Block Diagram

Normal Operation Mode

TPA0

2 Block Diagram Asynchronous Transmit Fifo Extended Mode

Asynchronous Transmit Fifo Extended Mode

3 Block Diagram Asynchronous Receive Fifo Extended Mode

Asynchronous Receive Fifo Extended Mode

Function of Each Block

Pin Assignment

8 6 6 1

Corresponding Table of MB86617A Pin

Outline Drawing of Package

Pin Function

TPB1

IEEE1394 Interface

Tsvalida

Isochronous Interface

Dssclkb

Ierra

Ierrb

Dssclka

XCS

MPU Interface

Xreset

Other Pins

VDD

Power/GND Pin

Write Read

Internal Register

LSI Specification MB86617A

LSI Specification MB86617A

LSI Specification MB86617A

Register Name Reserved

LSI Specification MB86617A

Internal Register Function Description

LSI Specification MB86617A

BIT

Ode-control Register

Action

Flag & status Register

Function Indicates that the device is not in forced sleep

Instruction-fetch Register

Interrupt-factor 06h Interrupt-mask 08h Initial Value

Receive Acknowledge Indicate Register

Buffer Data Port Receive/Transmit

TSP Transmit Information Setting Register a

CP-IC

TSP Transmit Information Setting Register B

Does not mask port B input of TSP -IC interface

Transmit Offset Setting Register a

Transmit Offset Setting Register B

TV2B

TSP Receive Information Setting Register

TV1B

DSS

Outputs to port a when Tscmp bit0 is ‘1’

Port B

TV2B TV1B

1Eh

28h

Fifo

TSP Status Register

TSP

Value Function

Data Bridge Transmit Information Setting Register 1 a

TSF

Data Bridge Transmit Information Setting Register 2 a

Data Bridge Transmit Information Setting Register 3 B

Data Bridge Transmit Information Setting Register 4 B

Data Bridge Receive Information Setting Register

SPB SPA

Transmit Packet Link/Split Setting Register

Dbqb

Dbqa

With more than 3 SP, executes according to setting

Late Packet Decision Range Setting Register a

Late Packet Decision Range Setting Register B

Receiv e Isochronous Packet Header Indicate Register 1 a

Receive Isochronous Packet Header Indicate Register 2 a

Receive Isochronous Packet Header Indicate Register 3 B

Receive Isochronous Packet Header Indicate Register 4 B

Fifo Reset Setting Register

BRG

Data Bridge Transmit/Receive Status Register a

Rx dlen-err-A

DV=‘00000’, MPEG2=‘10000’ or DSS=‘100001’

EMI

Data Bridge Transmit/Receive Status Register B

Rx dlen-err-B

Rx CIP err-B

Isochronous Channel Monitor Register

Cycle-timer-monitor Indicate Register

Ping Time Monitor Register

PHY/LINK Register/Address Setting Register

PHY/LINK

PHY/LINK Register Access Port

Revision Indicate Register

TSCHA-2

Transmit CGMS/TSCH Indicate Register a

CGMSA-2

TSCHA-1

TSCHB-2

Transmit CGMS/TSCH Indicate Register B

CGMSB-2

CGMSB-1 TSCHB-1

TSC

Transmit CGMS/TSCH Indicate Status Register

Finally input from port a at TSP IC I/F

IPH EMI-A

Transmit EMI/OE Setting Register

IPH EMI-B

Bridge-Ach

PHY/INK Register Function Description

PHY/LINK Register Table

Write Read

Description of Each Bit

Physical register #00 read

Physical register #01 read/write

Physical register #02 read

Physical register #03 read

Physical register #04 read/write

Isbr

Physical register #05 read/write

Is set at ‘1’

Physical register #07, 08, 09 read

Physical register #0A, 0B, 0C read/write

Physical register #0D, 0E, 0F read/write

Physical register #10 read

Physical register #11, 12, 13 read

Physical register #14, 15, 16 read

Physical register #17, 18, 19, 1A, 1B, 1C, 1D, 1E read/write

Link register #00 read/write

Link register #01 read/write

Link register #02 read/write

Link register #03 read/write

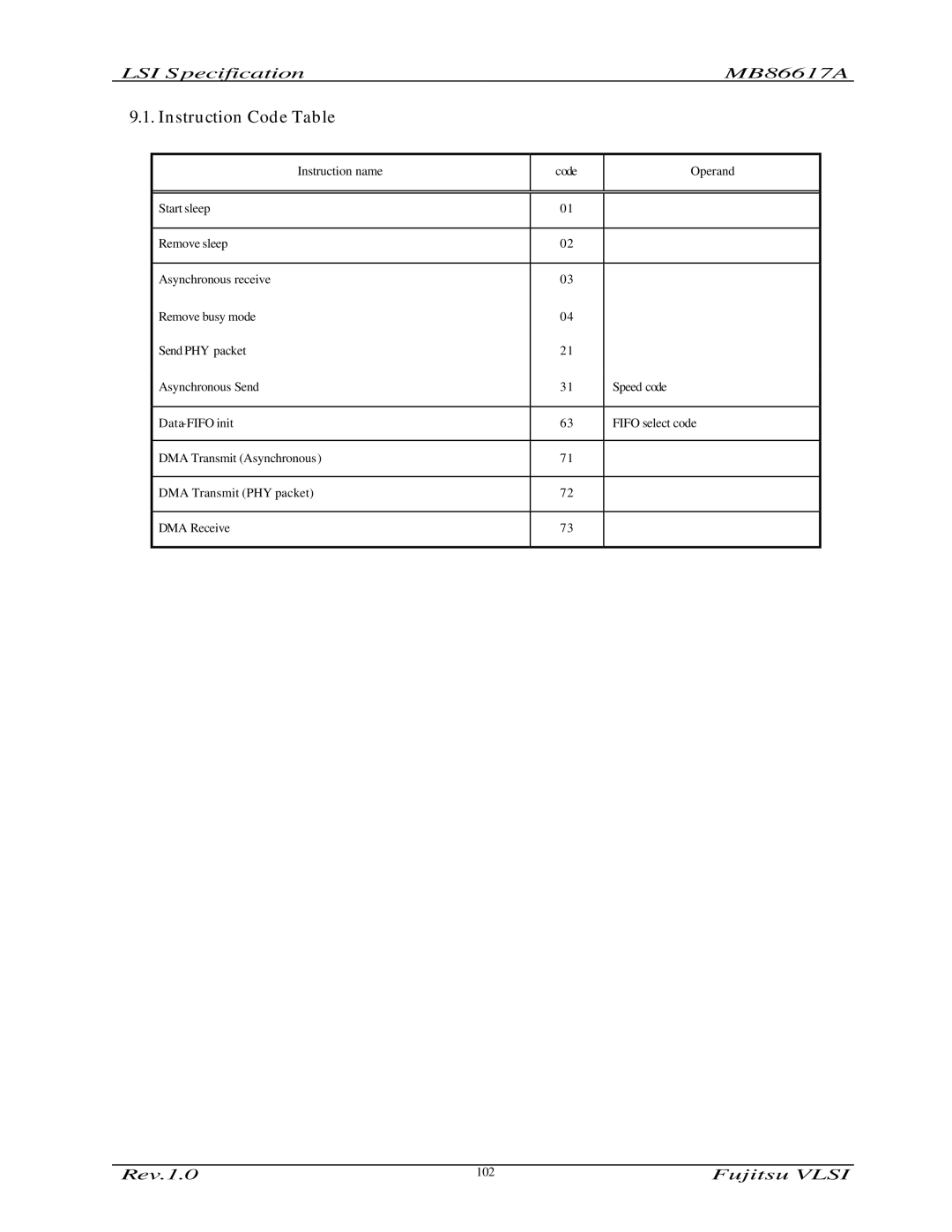

Instruction

Instruction Code Table

Start sleep 01 h

Description of Each Instruction

Asynchronous Send 31 h

DMA Transmit Asynchronous 71h

Interrupt

Intial Value ‘0’

Interrupt Interrupt Item

Description of Interrupt

INT10

INT7

INT8

INT9

INT26

INT23

INT24

INT25

Operation

Start

Initialization

Self-ID Packet Receiving

Self-ID Packet Receive at Bus Reset Process

Flow chart before bus reset completion

Flow chart after bus reset completion

Self-ID Packet Receive after Transmitting Ping Packet Ping

Flow chart after receiving Self-ID packet

Asynchronous Packet Transmitting

121

Asynchronous Packet Receiving

123

124

Isochronous Packet Transmitting

126

127

Isochronous Packet Receiving

129

System Configuration

56ョ

Recommended Connection for Cable Power Supply

FIL

Configuration of Feedback Circuit at Crystal Oscillator