Intel StrongARM SA-1100 Microprocessor

Developer’s Manual

SA-1100 Developer’s Manual

Contents

Caches, Write Buffer, and Read Buffer

Memory-Management Unit MMU

1.6

System Control Module

Reviving the DRAMs from Self-Refresh Mode

Memory and Pcmcia Control Module

Peripheral Control Module

11-39

11.8.3.4Endpoint 0 Interrupt Mask EIM 11-64 11.8.3.5Receive

11-81

SA-1100 Developer’s Manual

11-128

Serial Port 4 MCP / SSP

11-169

11.12.12.1Transmit Fifo Not Full Flag TNF

Internal Test

Register Summary MHz Oscillator Specifications

KHz Oscillator Specifications

Figures

SA-1100 Power and Clock Supply Sources and States

Tables

14-4

Page

Introduction

Intel StrongARM SA-1100 Microprocessor

LCD

DMA

Features of the SA-1100 CPU for AA and EA Parts

Features of the SA-1100 CPU for CA and DA Parts

Additional Features Built into SA-1100 Chipset

Changes to the SA-1100 Core from the SA-110

Overview

Example System

SA-1100 Example System

ARM Architecture

Write Buffer

Read Buffer

Page

Block Diagram

Functional Description

SA-1100 Block Diagram

Inputs/Outputs

Name Type Description

Signal Description

Signal Descriptions Sheet 1

Signal Descriptions Sheet 2

Signal Descriptions Sheet 3

TDO OCZ

VDD

VSS

Memory Map

1GB

Pcmcia Interface Mbyte Static Memory ROM, Flash, Sram

Exceptions

ARM Implementation Options

Big and Little Endian

Power-Up Reset

ROM Size Select

Abort

Address Exception Mode on Entry

Vector Summary

Exception Priorities

Vector Summary

Interrupt Latencies and Enable Timing

Coprocessors

Page

Instruction Group Result Delay Issue Cycles

Instruction Set

Instruction Set

Instruction Timings

Page

Coprocessors

Internal Coprocessor Instructions

Coprocessor 15 Definition

Register 0 ID

Cache and MMU Control Registers Coprocessor

Register Register Reads Register Writes

Register 1 Control

Register 3 Domain Access Control

Register 5 Fault Status

Register 6 Fault Address

Register 2 Translation Table Base

Register 7 Cache Control Operations

Register 8 TLB Operations

Function

OPC2

Register 9 Read-Buffer Operations

Registers 10 12 Reserved

CRm

Access process ID register 0b000 0b0000

Register 13 Process ID Virtual Address Mapping

Register 14 Debug Support Breakpoints

Dbcr Bit Action

Register 15 Test, Clock, and Idle Control

0b010 0b0100 Wait for interrupt 0b1000

Page

Caches, Write Buffer, and Read Buffer

Instruction Cache Icache

Icache Operation

Icache Validity

Icache Enable/Disable and Reset

Data Caches Dcaches

Enabling the Icache

Disabling the Icache

Cacheable Bit C

Bufferable Bit B

Cacheable Reads C =

Noncacheable Reads C =

Doubly Mapped Space

Dcaches Enable/Disable and Reset

Software Dcache Flush

Write Buffer Operation

Write Buffer WB

Bufferable Bit

Read Buffer RB

Enabling the Write Buffer

Writes to a Bufferable and Noncacheable Location B=1,C=0

Unbufferable Writes B=0

Caches, Write Buffer, and Read Buffer

Page

MMU Faults and CPU Aborts

Memory-Management Unit MMU

Data Aborts

MMU Registers

Interaction of the MMU, Icache, Dcache, and Write Buffer

Cacheable Reads Linefetches

Buffered Writes

Valid MMU, Dcache, and Write Buffer Combinations

To disable the MMU

Mini Data Cache

Page

Clocks

SA-1100 Crystal Oscillators

RTC

ARM

Core Clock Configuration Register

Restrictions on Changing the Core Clock Configuration

Core Clock Configurations

CCF40 Core Clock Frequency in MHz MHz Crystal Oscillator

Driving SA-1100 Crystal Pins from an External Source

Clocking During Test

System Control Module

General-Purpose I/O

Gpio Register Definitions

Gpio Pin Edge Detect

Gpio Pin-Level Register Gplr

Bit Name Description

Bit Reset

Gpio Pin Direction Register Gpdr

PS9 PS8 PS7 PS6 PS5 PS4 PS3 PS2 PS1 PS0

31..28 Reserved

Bit Name Description Gpio Rising-Edge Detect Register Grer

Bit Name Description Gpio Falling-Edge Detect Register Grer

Gpio Edge Detect Status Register Gedr

Gpio Alternate Function Register Gafr

Pin Alternate Function Direction Unit Signal Description

Gpio Alternate Functions

Gpio Register Locations

Address Name Description

Interrupt Controller

Interrupt Controller Register Definitions

Interrupt Bits

Interrupt

Bit Field Description

Interrupt Controller Pending Register Icpr

Bit Position Unit Source Module

IP9 IP8 IP7 IP6 IP5 IP4 IP3 IP2 IP1 IP0

IMn Interrupt mask n where n = 0 through

Interrupt Controller Mask Register Icmr

Interrupt Controller Level Register Iclr

Bit Name

Disable idle mask

Idle mode. This bit is cleared during all resets

Interrupt Controller Control Register Iccr

DIM

RTC Counter Register Rcnr

Real-Time Clock

Interrupt Controller Register Locations

RTC Alarm Register Rtar

RTC Status Register Rtsr

ALE

HZE

Oscillator Frequency Calibration

Trim Procedure

RTC Trim Register Rttr

Rttr Value Calculations

Trim Example #1 Measured Value Has No Fractional Component

Operating System Timer

Real-Time Clock Register Locations

OS Timer Count Register Oscr

OS Timer Match Registers 0-3 OSMR0, OSMR1, OSMR2, OSMR3

OS Timer Watchdog Match Enable Register Ower

WME

OS Timer Status Register Ossr

Interrupt enable channel

OS Timer Interrupt Enable Register Oier

Watchdog Timer

OS Timer Register Locations

OS Timer Register Locations

Power Manager

Run Mode

Idle Mode

Entering Idle Mode

Sleep Mode

Exiting Idle Mode

CPU Preparation for Sleep Mode

Events Causing Entry into Sleep Mode

Sleep Wake-Up Sequence

During Sleep Mode

Sleep Shutdown Sequence

Booting After Sleep Mode

Assumed Behavior of an SA-1100 System in Sleep Mode

Reviving the DRAMs from Self-Refresh Mode

Idle Sleep

Hardware Reset

RUN

Pin Name Type

Pin Operation in Sleep Mode

Pin State During Step

Power Manager Registers

Power Manager Control Register Pmcr

Power Manager General Configuration Register Pcfr

Opde

Power Manager PLL Configuration Register Ppcr

Power Manager Wake-Up Enable Register Pwer

WEn

VFS

Power Manager Sleep Status Register Pssr

BFS

Bit is cleared. This bit is cleared on hardware reset

Dram control hold

Peripheral control hold

31..5 Reserved

Power Manager Scratch Pad Register Pspr

Power Manager Gpio Sleep State Register Pgsr

Power Manager Register Locations

Power Manager Register Locations

Power Manager Oscillator Status Register Posr

Reset Controller

Hardware reset

Reset Controller Registers

Reset Controller Software Reset Register Rsrr

Software reset

SWR

Reset Controller Register Locations

Reset Controller Register Locations

Reset Controller Status Register Rcsr

Page

Memory and Pcmcia Control Module

Overview of Operation

Intel

SA-1100 Memory Controller Interface

Memory and Pcmcia Control Module

10-2

Example Memory Configuration

Example Memory System

Types of Memory Accesses

Reads

Writes

Transaction Summary

Read-Lock-Write

Aborts and Nonexistent Memory

SA-1100 Transactions

Bus Operation

Memory Interface Control Registers

Memory Configuration Registers

Physical Address Symbol Register Name

Dram Configuration Register Mdcnfg

CDB2

31..17 DRI140 Dram refresh interval

Cycle

Mem clock frequency /4

Will not be interrupted

Dram CAS Waveform Shift Registers MDCAS0, MDCAS1, MDCAS2

ROM or the first access of a burst ROM

For Flash and SRAM, this determines the read access time

Static Memory Control Registers MSC1-0

One memory clock cycle is added to this value

For Flash and SRAM, this determines the write pulse width

12..8 RDNx40 ROM delay next access

Accesses of a burst ROM

Expansion Memory Pcmcia Configuration Register Mecr

BSxx Bit Encoding

Bclk Speeds for 160-MHz Processor Core Frequency

Bclksel

Bclk Cycle Time-ns

Dynamic Interface Operation

Dram Overview

Dram Memory Size Options

Dram Row/Column Address Multiplexing

Dram Timing

Addr

Mdcnfgtrp = 4 MDCNFGCDB2 =

Dram Burst-of-Eight Transactions

Dram Self-Refresh in Sleep Mode

Static Memory Interface

Dram Refresh

10-18

ROM Timing Diagrams and Parameters

ROM Interface Overview

A255

A42

Input Data Latch

10-20

Eight Beat Burst Read from Burst-of-Four ROM

SA-1100 Developer’s Manual

Sram Interface Overview

Sram Timing Diagrams and Parameters

Sram Write Timing Diagram 4-Beat Burst

Flash Eprom Interface Overview

Flash Eprom Timing Diagrams and Parameters

10-24

Static Access Followed by a Dram Access

Dram Access Followed by a Static Access

Dram Access Followed by a Refresh Operation

General Memory BUS Timing

Pcmcia Overview

10-26

10.6.1 32-Bit Data Bus Operation

Address

External Logic for Pcmcia Implementation

10-28

12. Pcmcia External Logic for a Two-Socket Configuration

13. Pcmcia External Logic for a One-Socket Configuration

10-30

Pcmcia Interface Timing Diagrams and Parameters

14. Pcmcia Voltage-Control Logic

15. Pcmcia Memory or I/O 16-Bit Access

10-32

16. Pcmcia I/O 16-Bit Access to 8-Bit Device

10-34

Flow of Events After Reset or Exiting Sleep Mode

Initialization of the Memory Interface

Alternate Memory Bus Master Mode

Page

Peripheral Control Module

Read/Write Interface

Memory Organization

Peripheral Register Width DMA Burst Size

Peripheral Units’ Base Addresses

Peripheral Serial Protocol Base Address

LCD Controller 0h B010 Serial Port

ICP Hssp

Interrupts

Peripheral Units’ Interrupt Numbers

Interrupt

Peripheral

Peripheral Gpio Pin Function

Peripheral Pins

Dedicated Peripheral Pins

Use of the Gpio Pins for Alternate Functions

Peripheral Unit Gpio Pin Assignment

DMA Controller

DMA Register Definitions

DMA Device Address Register DDARn

Device From To Half-word wide To From Byte-wide

D31 D0 1 0 from memory

Controller From Half-word wide

11-10

Valid Settings for the DDARn Register

Ddar Fields Unit Name Function Address DA318 DS30

DMA Control/Status Register DCSRn

DMA Buffer a Start Address Register DBSAn

DMA Buffer a Transfer Count Register DBTAn

DMA Operation

DMA Buffer B Start Address Register DBSBn

DMA Buffer B Transfer Count Register DBTBn

TCB120 Transfer count buffer B

Physical Address Register Name Symbol

DMA Register List

DBSA3

DBTA3

DBSB3

DBTB3

LCD Controller

11-16

Lpclk

LCD Controller Operation

DMA to Memory Interface

Frame Buffer

11-18

PBS

13..12

Pixel bit size

To palette

Frame to palette

Encoded Pixel Data150

Encoded Pixel Data70 Bit

Unused Red Data30 Green Data30 Blue Data30

FrameBufferSize = 32 + 16 + è

11-22

Input Fifo

Lookup Palette

Color/Gray-Scale Dithering

Output Fifo

Color/Gray-Scale Intensities and Modulation Rates

Dither Value Intensity Modulation Rate

LCD Controller Pins

LCD Controller Register Definitions

LCD Enable LEN

LCD Controller Control Register

Color/Monochrome Select CMS

Single-/Dual-Panel Select SDS

Dual Panel Active Panel

Single Passive Screen Portion Pins

LCD Controller Data Pin Utilization

LCD Data-Pin Pixel Ordering

11-28

LCD Disable Done Interrupt Mask LDM

Base Address Update Interrupt Mask BAM

Error Interrupt Mask ERM

Passive/Active Display Select PAS

11-30

11.7.3.8 Big/Little Endian Select BLE

Double-Pixel Data DPD Pin Mode

Palette DMA Request Delay PDD

LEN

CMS

SDS

LDM

PAS

BLE

DPD

PDD

Pixels Per Line PPL

Horizontal Sync Pulse Width HSW

End-of-Line Pixel Clock Wait Count ELW

11-34

Beginning-of-Line Pixel Clock Wait Count BLW

PPL

HSW

ELW

11-36

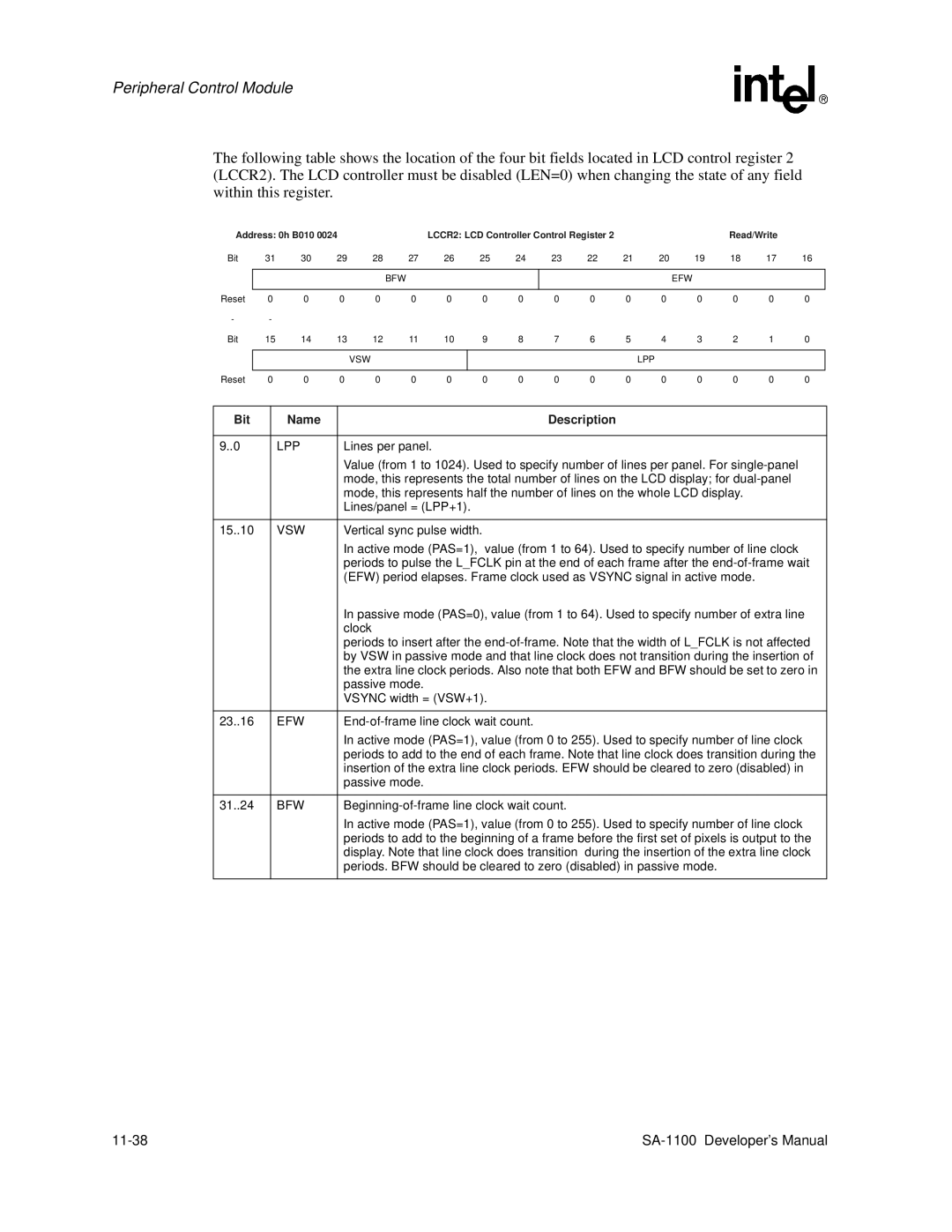

Lines Per Panel LPP

Vertical Sync Pulse Width VSW

End-of-Frame Line Clock Wait Count EFW

Beginning-of-Frame Line Clock Wait Count BFW

LPP

VSW

EFW

BFW

Pixel Clock Divider PCD

AC Bias Pin Frequency ACB

AC Bias Pin Transitions Per Interrupt API

Vertical Sync Polarity VSP

Horizontal Sync Polarity HSP

Pixel Clock Polarity PCP

Output Enable Polarity OEP

Address 0h B010

LCD Controller DMA Registers

HSP

PCP

OEP

DMA Channel 1 Base Address Register

31..0

DBAR1

DMA channel 1 base address pointer

DMA Channel 1 Current Address Register

DCAR1

DMA channel 1 current address pointer

Equal to the calculated end address of the buffer

DMA Channel 2 Base and Current Address Registers

DBAR2

DCAR2

DMA channel 2 current address pointer

LCD Disable Done Flag LDD read/write, maskable interrupt

Base Address Update Flag BAU read-only, maskable interrupt

Bus Error Status BER read/write, maskable interrupt

LCD Controller Status Register

AC Bias Count Status ABC read/write, nonmaskable interrupt

LDD

BAU

BER

ABC

IOL

IUL

LCD Controller Register Locations

LCD Controller Control, DMA, and Status Register Locations

LCD Controller Pin Timing Diagrams

LDDx0

11-52

Lfclk Llclk Lpclk

LDDx0

12. Passive Mode Pixel Clock and Data Pin Timing

DPD =

13. Active Mode Timing

11-54

14. Active Mode Pixel Clock and Data Pin Timing

11-56

Serial Port 0 USB Device Controller

USB Operation

Signalling Levels

10. USB Bus States

Bus State UDC+/UDC- Pin Levels

Port

11-58

Bit Encoding

Bit Value Digital Data Nrzi Data

Field Formats

11. Endpoint Field Addressing

Endpoint Field Value UDC Endpoint Selected

Endpoint

Packet Formats

PID

CRC5

CRC16

Transaction Formats

Action

OUT

Packets from UDC to host are boldface

Setup DATA0

UDC Device Requests

Action Token Packet Data Packet

11-62

Request Name

UDC Register Definitions

12. Host Device Request Summary

UDC Control Register

Reset Interrupt Mask REM

Suspend/Resume Interrupt Mask SRM

Address 0h 8000

Udccr

UDC Address Register

UDC OUT Max Packet Register

Udcar

Udcomp

Udcimp

UDC in Max Packet Register

Address 0h 8000 000C

UDC Endpoint 0 Control/Status Register

Serviced Setup End SSE

UDCCS0

SSE FST SST IPR OPR

SSE

Receive Fifo Service RFS

Receive Packet Error RPE

UDC Endpoint 1 Control/Status Register

Receive Packet Complete RPC

Bits 7..6 Reserved

UDCCS1

RNE FST SST RPE RPC RFS

RNE

Transmit Fifo Service TFS

Transmit Packet Error TPE

UDC Endpoint 2 Control/Status Register

Transmit Packet Complete TPC

UDCCS2

FST SST TUR TPE TPC TFS

UDC Endpoint 0 Data Register

UDC Endpoint 0 Write Count Register

UDCD0

Data

UDC Data Register

Uddr

Top/bottom of transmit/receive Fifo data

Read Bottom of receive Fifo data

UDC Status/Interrupt Register

Reset Interrupt Request Rstir

Udcsr

Rstir Resir Susir TIR RIR EIR

Rstir

13. UDC Control, Data, and Status Register Locations

Serial Port 1 SDLC/UART

UDC Register Locations

Sdlc Operation

Frame Format

Address Field

Control Field

CRC-CCITT

Baud Rate Generation

Data Field

CRC Field

Receive Operation

11-82

Transmit Operation

Simultaneous Use of the Uart and Sdlc

CPU and DMA Register Access Sizes

Sdlc Register Definitions

Transmit and Receive FIFOs

11-84

Loopback Mode LBM

Sdlc Control Register

SDLC/UART Select SUS

Single/Double Flag Select SDF

Sample Clock Enable SCE

Bit Modulation Select BMS

Sample Clock Direction SCD

11-86

Receive Clock Edge Select RCE

Transmit Clock Edge Select TCE

Address 0h 8002

SDCR0

Abort After Frame AAF

TCE

Transmit Enable TXE

Receive Enable RXE

Receive Fifo Interrupt Enable RIE

Transmit Fifo Interrupt Enable TIE

Address Match Enable AME

Receiver Abort Interrupt EnableRAE

Transmit Fifo Underrun Select TUS

11-90

SDCR1

Read/Write

RAE TUS AME TIE RIE RXE TXE AAF

RAE

AMV

Address Match Value AMV

SDCR2

Sdlc Control Registers 3

Baud Rate Divisor BRD

Address 0h 8002 006C

SDCR3

Sdlc Data Register

11-94

Address 0h 0078

Sddr

ROR CRE EOF

ROR

Sdlc Status Register

Transmit Underrun Status TUR read/write, maskable interrupt

Receiver Abort Status RAB read/write, maskable interrupt

11-96

SA-1100 Developer’s Manual 11-97

SDSR0

RFS TFS RAB TUR EIF

Receiver Synchronized Flag RSY read-only, noninterruptible

Transmitter Busy Flag TBY read-only, noninterruptible

Receive Fifo Not Empty Flag RNE read-only, noninterruptible

Transmit Fifo Not Full Flag TNF read-only, noninterruptible

11-100

CRC Error Status CRE read-only, noninterruptible

Receiver Overrun Status ROR read-only, noninterruptible

SDSR1

ROR CRE EOF RTD TNF RNE

RSY

TBY

Uart Register Locations

14. Uart Control, Data, and Status Register Locations

15. Sdlc Control, Data, and Status Register Locations

Serial Port 2 Infrared Communications Port ICP

Sdlc Register Locations

Low-Speed ICP Operation

HP-SIR*Modulation

Uart Frame Format

11-104

Chip Timeslots Data =

High-Speed ICP Operation

11.10.2.1 4PPM Modulation

Hssp Frame Format

SA-1100 Developer’s Manual 11-107

11-108

SA-1100 Developer’s Manual 11-109

11-110

HP-SIR Enable HSE

Low-Power Mode LPM

Uart Register Definition

Uart Control Register

Hssp Register Definitions

Hssp Control Register

IrDA Transmission Rate ITR

LPM

SA-1100 Developer’s Manual 11-113

11-114

AME TIM RIM RXE TXE TUS LBM ITR

Address 0h 8004

HSCR0

11-116

HSCR1

Search for the next preamble

Transmit Pin Polarity Select TXP

Receive Pin Polarity Select RXP

0h 9006

HSCR2

RXP TXP

RXP

Hssp Data Register

Address 0h 8004 006C

Hsdr

Last Fifo entry is transferred to the ROR bit

HSSR1

Hssp Status Register

Receiver Abort Status RAB read/write, nonmaskable interrupt

11-122

Framing Error Status FRE read/write, nonmaskable interrupt

HSSR0

FRE RFS TFS RAB TUR EIF

FRE

End-of-Frame Flag EOF read-only, noninterruptible

11-124

SA-1100 Developer’s Manual 11-125

HSSR1

ROR CRE EOF TNF RNE TBY RSY

17. Hssp Control, Data, and Status Register Locations

Hssp Register Locations

16. Uart Control, Data, and Status Register Locations

Serial Port 3 Uart

Uart Operation

LSB MSB

11-128

30. NRZ Bit Encoding Example 0100

11-130

11.11.3.2 Odd/Even Parity Select OES

Parity Enable PE

Uart Register Definitions

11-132

Stop Bit Select SBS

Data Size Select DSS

UTCR0

TCE RCE SCE DSS SBS OES

Bit Reset BRD70

Uart Control Registers 1

UTCR1

UTCR2

Break BRK

Receiver Enable RXE

Transmitter Enable TXE

UTCR3

LBM TIE RIE BRK TXE RXE

Uart Data Register

Utdr

ROR FRE PRE

Uart Status Register

11-140

Error in Fifo Flag EIF read-only, nonmaskable interrupt

Receiver Idle Status RID read/write, maskable interrupt

EIF REB RBB RID RFS TFS

Address 0h 8005 001C

UTSR0

Parity Error Flag PRE read-only, noninterruptible

11-142

Framing Error Flag FRE read-only, noninterruptible

Receiver Overrun Flag ROR read-only, noninterruptible

ROR FRE PRE TNF RNE TBY

UTSR1

Read-Only

Serial Port 4 MCP / SSP

MCP Operation

11-146

31. MCP Frame Data Format

Audio and Telecom Sample Rates and Data Transfer

11-148

MCP Transmit and Receive Fifo Operation

11-150

Codec Control Register Data Transfer

Bit Audio Data Telecom Data

External Clock Operation

Alternate SSP Pin Assignment

MCP Register Definitions

MCP Control Register

Audio Sample Rate Divisor ASD

11-152

Telecom Sample Rate Divisor TSD

Multimedia Communications Port Enable MCE

11.12.3.5 A/D Sampling Mode ADM

External Clock Select ECS

11-154

Telecom Transmit Fifo Interrupt Enable TTE

Telecom Receive Fifo Interrupt Enable TRE

Audio Transmit Fifo Interrupt Enable ATE

Audio Receive Fifo Interrupt Enable are

External Clock Prescaler ECP

ASD

Audio sample rate divisor

TSD

MCE

ECS

ADM

TTE

CFS

MCP Data Registers

Clock Frequency Select CFS

MCP Data Register

Address 0h 8006 MCP Data Register 0 MCDR0 Read/Write

Reserved for future enhancements

15..4

Address 0h 8006 000C MCP Data Register 1 MCDR1 Read/Write

SA-1100 Developer’s Manual 11-161

Reg Address R/W Reset Bit

Address 0h 8006 MCP Data Register 2 MCDR2 Read/Write

15..0 Codec

Register read Read/write Read Returns a zero

MCP Status Register

11-164

SA-1100 Developer’s Manual 11-165

Audio Codec Enabled Flag ACE read-only, noninterruptible

Telecom Codec Enabled Flag TCE read-only, noninterruptible

Codec Write Completed Flag CWC read-only, noninterruptible

Codec Read Completed Flag CRC read-only, noninterruptible

ATS

ARS

TTS

TRS

TTU

TRO

ANF

ANE

SSP Operation

35. Texas Instruments* Synchronous Serial Frame Format

11-170

36. Motorola* SPI Frame Format

37. National Microwire* Frame Format

11-172

SSP Transmit and Receive FIFOs

Bit Bit Data

11-174

SSP Register Definitions

SSP Control Register

Synchronous Serial Port Enable SSE

Frame Format FRF

SCR

Serial Clock Rate SCR

FRF

Serial Clock Polarity SPO

Serial Clock Phase SPH

Sclk SPO=0 Sclk SPO=1 Sfrm TXD4 RXD4

LSB

11-178

SPO

Justifies data and zero fills unused bits 11-180

SSP Data Register

Address 0h 8007 006C

SSP Status Register

SSP Busy Flag BSY read-only, noninterruptible

BSY

MCP Register Locations

SSP Register Locations

19. MCP Control, Data, and Status Register Locations

20. SSP Control, Data, and Status Register Locations

11-184

Peripheral Pin Controller PPC

PPC Operation

PPC Register Definitions

PPC Pin Direction Register

Sclk

PPC Pin State Register

Address 0h 9006 Ppsr PPC Pin StateRegister Read/Write

LCD pixel clock pin state

Read Current state of LCD pixel clock pin returned

LCD line clock pin state

Read Current state of LCD line clock pin returned

PPC Pin Assignment Register

Uart Pin Reassignment UPR

SSP Pin Reassignment SPR

UPR

PPC Sleep Mode Pin Direction Register

11-190

LCD pixel clock sleep mode pin direction

LCD pixel clock pin configured as input during sleep

LCD line clock sleep mode pin direction

LCD line clock pin configured as input during sleep

PPC Pin Flag Register

PPC Register Locations

21. PPC Control and Flag Register Locations

Page

Symbol Parameter Min Max Units

DC Parameters

Absolute Maximum Ratings

SA-1100 DC Maximum Ratings

Symbol Parameter Min Nom Max Units

DC Operating Conditions

SA-1100 DC Operating Conditions

× Vddx

Power Supply Voltages and Currents

Parameter SA-1100 Units

VDD

Vddx

Page

SA-1100 Output Derating

AC Parameters

Test Conditions

Memory Bus and Pcmcia Signal Timings

Module Considerations

Memory Bus Memory Bus Out

13-2

LLDD70 fall

LCD Controller Signals

MCP Signals

Pin Name Symbol Parameter Min Max Unit

Timing Parameters

SA-1100 AC Timing Table for AA and BA Parts

Sfrmc

Asynchronous Signal Timing Descriptions

Page

Package and Pinout

Mechanical Data and Packaging Information

SA-1100 Pinout 208-Pin Quad Flat Pack

14-2

Mini-Ball Grid Array mBGA

SA-1100 256 Mini-Ball Grid Array Mechanical Drawing

SA-1100 Pinout 256-Pin Mini-Ball Grid Array

14-4

Data Breakpoint

Debug Support

Instruction Breakpoint

Page

Test Access Port TAP Controller State Transitions

Boundary-Scan Test Interface

Reset

Pull-Up Resistors

Instruction Register

Public Instructions

Clamp

Extest

SAMPLE/PRELOAD

Highz

Idcode

Bypass

16-4

Test Data Registers

Bypass Register

16-6

16.6.2 SA-1100 Device Identification ID Code Register

16.6.3 SA-1100 Boundary-Scan BS Register

Boundary-Scan Interface Signals

Tbscl Tbsch

Tbsis Tbsih

Tbsoh Tbsod Data Tbsss Tbssh Data Out Tbsdh Tbsdd

Tbsoe

Data Out Tbsde

Tbsr

Tbsrs Tbsrh

Symbol Parameter Minimum Typical Maximum Units

SA-1100 Boundary-Scan Interface Timing

Page

Register Summary

Tucr

B000 0044

DMA control/status register 2 write ones to set

B000 0048 Write ones to clear 004C Read only 0050

B000 0054

Ucdomp

Sdlc Registers Serial Port 8002

8031

8003 Reserved 8003 001C

8004 007C 0h 8004 Ffff Reserved

9006 0034 0h 9006 Ffff Reserved

Uart Registers Serial Port 8005

8007 0078 0h 8007 Ffff Reserved PPC Registers 9006

System Specifications

MHz Oscillator Specifications B

Specifications

MHz Oscillator Specifications

Specification Minimum Typical Maximum Unit

Typical Maximum Unit

Quartz Crystal Specification

Specification

Page

KHz Oscillator Specifications C

Temperature Range

Current Consumption

Startup Time

Frequency Shift Due to Temperature Effect on the Circuit

Parasitic Capacitance Off-chip Between Txtal and Textal

Parasitic Resistance Between Txtal and Textal

Parasitic Resistance Between Txtal or Textal and VSS

Other providers supply a Quality Factor, Q, instead of Rm

Therefore, the values for Q

Corresponding to specified range of Rm are supplied

Following table

KHz Oscillator Specifications

PMD

Internal Test

Test Unit Control Register Tucr

TSEL2-0

TSEL2 TSEL1 TSEL0

Page

Support, Products, and Documentation