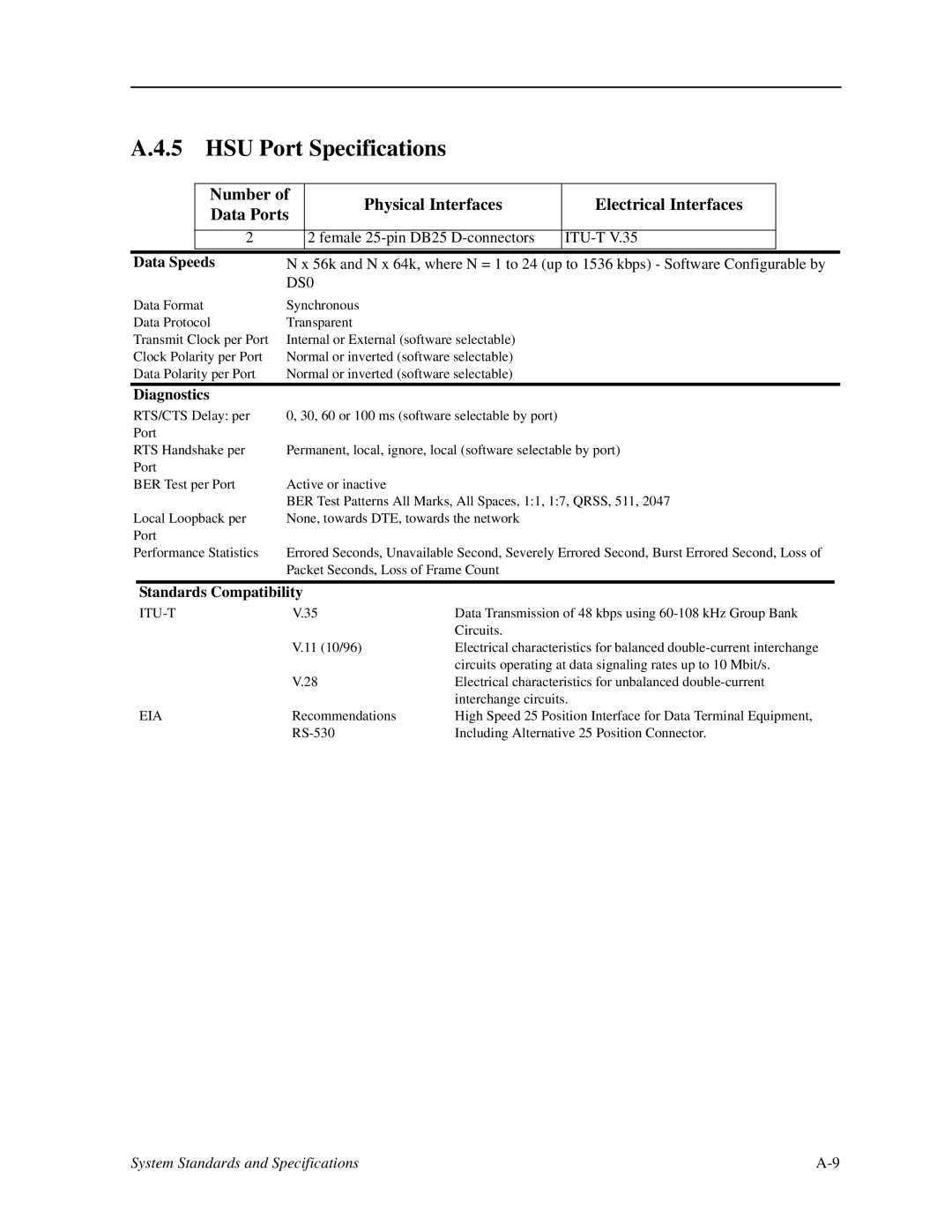

A.4.5 HSU Port Specifications

| Number of |

| Physical Interfaces | Electrical Interfaces |

| |

| Data Ports |

|

| |||

|

|

|

|

| ||

|

|

|

|

|

| |

| 2 |

| 2 female |

| ||

|

| |||||

Data Speeds | N x 56k and N x 64k, where N = 1 to 24 (up to 1536 kbps) - Software Configurable by | |||||

|

| DS0 |

|

|

| |

Data Format | Synchronous |

|

|

| ||

Data Protocol | Transparent |

|

|

| ||

Transmit Clock per Port | Internal or External (software selectable) |

|

| |||

Clock Polarity per Port | Normal or inverted (software selectable) |

|

| |||

Data Polarity per Port | Normal or inverted (software selectable) |

|

| |||

Diagnostics |

|

|

|

|

| |

RTS/CTS Delay: per | 0, 30, 60 or 100 ms (software selectable by port) |

|

| |||

Port |

|

|

|

|

| |

RTS Handshake per | Permanent, local, ignore, local (software selectable by port) | |||||

Port |

|

|

|

|

| |

BER Test per Port | Active or inactive |

|

| |||

|

| BER Test Patterns All Marks, All Spaces, 1:1, 1:7, QRSS, 511, 2047 | ||||

Local Loopback per | None, towards DTE, towards the network |

|

| |||

Port |

|

|

|

|

| |

Performance Statistics | Errored Seconds, Unavailable Second, Severely Errored Second, Burst Errored Second, Loss of | |||||

|

| Packet Seconds, Loss of Frame Count |

|

| ||

Standards Compatibility

| V.35 | Data Transmission of 48 kbps using |

|

| Circuits. |

| V.11 (10/96) | Electrical characteristics for balanced |

|

| circuits operating at data signaling rates up to 10 Mbit/s. |

| V.28 | Electrical characteristics for unbalanced |

|

| interchange circuits. |

EIA | Recommendations | High Speed 25 Position Interface for Data Terminal Equipment, |

| Including Alternative 25 Position Connector. |

System Standards and Specifications |