Compaq Computer Corporation Shrewsbury, Massachusetts

Revision/Update Information

21264/EV68A Hardware Reference Manual

Table of Contents

Cache and External Interfaces

Hardware Interface

Internal Processor Registers

Privileged Architecture Library Code

Mffpcr Mtfpcr

Initialization and Configuration

Thermal Management

Error Detection and Error Handling

Testability and Diagnostics

Electrical Data

21264/EV68A Boundary-Scan Register

Alpha Instruction Set

Glossary Index

21264/EV68A-to-Bcache Pin Interface

Figures

10-2 Type 2 Heat Sink

Tables

Xiv

VDD Idcpower

Page

Preface

Content

Audience

Documentation Included by Reference

For example

Terminology and Conventions

Abbreviations

Aligned and Unaligned

W1C

W1S

Addresses

External

Signal Names

Data Units

Do Not Care

Undefined

Do not care. a capital X represents any valid value

Page

Architecture

Introduction

Introduction

Floating-Point Data Types

Architecture

Addressing

Integer Data Types

21264/EV68A Microprocessor Features

21264/EV68A Microprocessor Features

21264/EV68A Microprocessor Features

21264/EV68A Microarchitecture

Internal Architecture

Internal Architecture

21264/EV68A Microarchitecture

Instruction Fetch, Issue, and Retire Unit

Virtual Program Counter Logic

Branch Predictor

21264/EV68A Block Diagram

Global Predictor

Local Predictor

Instruction-Stream Translation Buffer

Choice Predictor

Instruction Fetch Logic

Integer Issue Queue

Register Rename Maps

Hwret

Floating-Point Issue Queue

Exception and Interrupt Logic

Integer Execution Unit

Retire Logic

Integer Execution Unit-Clusters 0

PERR, MINxxx, MAXxxx, UNPKxx, PKxx

10Internal Architecture

Floating-Point Execution Unit

Onchip Caches

External Cache and System Interface Unit

21264/EV68A contains two onchip primary-level caches

Data Cache

Memory Reference Unit

12Internal Architecture

Miss address file MAF Dstream translation buffer DTB

Pipeline Organization

Pipeline Organization

Srom Interface

Stage 1 Instruction Slot

Stage 0 Instruction Fetch

14Internal Architecture

Stage 2 Map

Stage 3 Issue

Ebox and Fbox pipelines begin execution

Instruction Issue Rules

Instruction Issue Rules

Pipeline Aborts

Instruction Name, Pipeline, and Types

Instruction Group Definitions

Instruction Group Definitions and Pipeline Unit

Ebox Slotting

FTOIS, Ftoit

ITOFS, ITOFF, Itoft

U U L E L U E E L L E U

20Internal Architecture

Instruction Latencies

Instruction Class Latency in Cycles

Hwmfpr

Instruction Retire Rules

Instruction Retire Rules

Minimum Retire Latencies for Instruction Classes

BSR/JSR

Retire of Operate Instructions into R31/F31

Retire of Operate Instructions into R31/F31

Floating-Point Divide/Square Root Early Retire

Instructions Retired Without Execution

Load Instructions to R31 and F31

Load Instructions to R31 and F31

Prefetch with Modify Intent LDS Instruction

Load Hit Speculation

Special Cases of Alpha Instruction Execution

Special Cases of Alpha Instruction Execution

Prefetch, Evict Next LDQ and Hwldq Instructions

10 Pipeline Timing for Floating-Point Load Instructions

Cmov Instruction

Floating-Point Store Instructions

26Internal Architecture

2 I/O Address Space Load Instructions

Memory and I/O Address Space Instructions

Memory and I/O Address Space Instructions

Memory Address Space Load Instructions

Rules for I/O Address Space Load Instruction Data Merging

Memory Address Space Store Instructions

28Internal Architecture

Rules for I/O Address Space Store Instruction Data Merging

4 I/O Address Space Store Instructions

Instruction Ordering

MAF Memory Address Space Merging Rules

MAF Memory Address Space Merging Rules

Replay Traps

Replay Traps

Mbox Order Traps

Memory Barrier MB/WMB/TB Fill Flow

12 I/O Write Buffer and the WMB Instruction

Write Buffer and the WMB Instruction

Other Mbox Replay Traps

WMB Instruction Processing

MB Instruction Processing

34Internal Architecture

TB Fill Flow

12 TB Fill Flow Example Sequence

13 TB Fill Flow Example Sequence

Floating-point control register Fpcr is shown in Figure

Performance Measurement Support-Performance Counters

Floating-Point Control Register

Performance Measurement Support-Performance Counters

14 Floating-Point Control Register Fields

Floating-Point Control Register

36Internal Architecture

Amask and Implver Instruction Values

Amask and Implver Instruction Values

Implver

Design Examples

Design Examples

Amask

12 Typical Uniprocessor Configuration

Page

Hardware Interface

21264/EV68A Microprocessor Logic Symbol

Hardware Interface

21264/EV68A Microprocessor Logic Symbol

21264/EV68A Microprocessor Logic Symbol

21264/EV68A Signal Descriptions

21264/EV68A Signal Names and Functions

21264/EV68A Signal Names and Functions

Signal Pin Types Definitions

Dcokh

Pllvdd

TestStatH

21264/EV68A Signal Descriptions by Function

SysVref Domain SysAddInL140

Pin Assignments

Pin List Sorted by Signal Name

Pin Assignments

AC1

Pllvdd

10Hardware Interface

AA5

12Hardware Interface

Pin List Sorted by PGA Location

SysDataL28

14Hardware Interface

BcDataH70 SysDataL5

16Hardware Interface

Ground and Power VSS and VDD Pin List

Mechanical Specifications

Mechanical Specifications

21264/EV68A Packaging

21264/EV68A Packaging

18Hardware Interface

21264/EV68A Bottom View Pin Up

Page

Introduction to the External Interfaces

Cache and External Interfaces

Cache and External Interfaces

Introduction to the External Interfaces

21264/EV68A System and Bcache Interfaces

System Interface

Second-Level Cache Bcache Interface

Commands and Addresses

Physical Address Considerations

Physical Address Considerations

MB/WMB

ECB I/O

Physical Address Considerations

System Duplicate Tag Stores

Bcache Interface Signals

Bcache Structure

Bcache Structure

Cache Coherency Basics

Victim Data Buffer

Cache Coherency

Victim Data Buffer

21264/EV68A-Supported Cache Block States

Cache Coherency

Cache Block States

2lists the cache block states supported by the 21264/EV68A

Cache Block State Transitions

Mands. -4lists these commands

System Responses to 21264/EV68A Commands

Cache Block State Transitions

System Responses to 21264/EV68A Commands and Reactions

Using SysDc Commands

12Cache and External Interfaces

Dcache States and Duplicate Tags

Lock Mechanism

Lock Mechanism

14Cache and External Interfaces

Internal Eviction of LDxL Blocks

In-Order Processing of LDxL/STxC Instructions

Liveness and Fairness

System Port

System Port

16Cache and External Interfaces

System Port Pins

System Port Pins

18Cache and External Interfaces

Programming the System Interface Clocks

Programming Values for System Interface Clocks

Program Values for Data-Sample/Drive CSRs

Bank Interleave on Cache Block Boundary Mode

3 21264/EV68A-to-System Commands

Forwarded Clocks and Frame Clock Ratio

12describes the field definitions for Tables 4-10and

Hit Mode

11 Page Hit Mode of Operation

12 21264/EV68A-to-System Command Fields Definitions

13 Maximum Physical Address for Short Bus Format

4 21264/EV68A-to-System Commands Descriptions

14describes the 21264/EV68A-to-system commands

14 21264/EV68A-to-System Commands Descriptions

22Cache and External Interfaces

15 Programming INVALTODIRTYENABLE10

24Cache and External Interfaces

ProbeResponse Commands Command40 =

16 Programming SETDIRTYENABLE20

17 21264/EV68A ProbeResponse Command

18describes the ProbeResponse command fields

SysAck and 21264/EV68A-to-System Commands Flow Control

18 ProbeResponse Fields Descriptions

RVB RPB

System-to-21264/EV68A Commands

Probe Commands Four Cycles

19 System-to-21264/EV68A Probe Commands

21 Data Movement Selection by Probe43

20 System-to-21264/EV68A Probe Commands Fields Descriptions

21 lists the data movement selected by Probe43

22lists the next cache block state selected by Probe20

23 Data Transfer Command Format

Data Transfer Commands Two Cycles

28Cache and External Interfaces

24 SysDc40 Field Description

24describes the SysDc40 field

8.1 21264/EV68A Clock Basics

Data Movement In and Out of the 21264/EV68A

30Cache and External Interfaces

Fast Data Mode

32Cache and External Interfaces

25 Sysclk Cycles Between SysAddOut and SysData

26 Cbox CSR SYSDCDELAY40 Examples

26shows four example configurations and shows their use

Fast Data Disable Mode

34Cache and External Interfaces

27 Four Timing Examples

SysDataInValidL and SysDataOutValidL

SysDataInValidL

SysFillValidL

SysDataOutValidL

28 Data Wrapping Rules

Data Wrapping

36Cache and External Interfaces

29 System Wrap and Deliver Data

30defines the interleaved scheme for the wrap order

30 Wrap Interleave Order

38Cache and External Interfaces

Nonexistent Memory Processing

31defines the wrap order for double-pumped data trans fers

31 Wrap Order for Double-Pumped Data Transfers

21264/EV68A Command NXM Address System/21264/EV68A Response

Ordering of System Port Transactions

10.1 21264/EV68A Commands and System Probes

40Cache and External Interfaces

System Port

Bcache Port

Bcache Port

36 Bcache Port Pins

Bcache Port Pins

35 Range of Maximum Bcache Clock Ratios

44Cache and External Interfaces

Bcache Clocking

38 BCCLKDELAY10 Values

37 BCCPUCLKDELAY10 Values

Setting the Period of the Cache Clock

46Cache and External Interfaces

39 Program Values to Set the Cache Clock Period Single-Data

41 Data-Sample/Drive Cbox CSRs

Bcache Transactions

Bcache Data Read and Tag Read Transactions

48Cache and External Interfaces

Bcache Data Write Transactions

Dual-data mode, bcfrm is twice the ratio

When the ratio is even, bcfrm is equal to the ratio

When the ratio is odd, bcfrm is twice the ratio

For example, in single-data mode

50Cache and External Interfaces

Pin Descriptions

Relationship Between Write-to-Read Bcwrrdbubbles and wrrd

Relationship Between Read-to-Write Bcrdwrbubbles and rdwr

BcAddH234

Bcache Control Pins

43 Programming the Bcache Control Pins

44 lists the combination of control pin assertion for

52Cache and External Interfaces

45 Control Pin Assertion for Ramtype B

46 Control Pin Assertion for Ramtype C

47 Control Pin Assertion for Ramtype D

Disabling the Bcache for Debugging

Bcache Banking

BcDataInClkH and BcTagInClkH

Interrupts

Interrupts

54Cache and External Interfaces

Internal Processor Registers

Internal Processor Registers

Mbox IPRs

Cycle Counter Control Register Ccctl

Ebox IPRs

Ebox IPRs

Cycle Counter Register CC

Cycle Counter Control Register Fields Description

Virtual Address Register VA

Virtual Address Control Register Vactl

2describes the Ccctl register fields

VAFORM32

Virtual Address Format Register Vaform

3describes the virtual address control register fields

Virtual Address Control Register Fields Description

ITB PTE Array Write Register Itbpte

Ibox IPRs

Ibox IPRs

ITB Tag Array Write Register Itbtag

ITB Invalidate All Register Itbia

ITB Invalidate All Process ASM=0 Register Itbiap

ITB Invalidate Single Register Itbis

ProfileMe PC Fields Description

ProfileMe PC Register Pmpc

Exception Address Register Excaddr

4describes the ProfileMe PC register fields

Instruction Virtual Address Format Register Ivaform

Interrupt Enable and Current Processor Mode Register Iercm

Iercm Register Fields Description

Software Interrupt Request Register Sirr

10Internal Processor Registers

6describes the software interrupt request register fields

Interrupt Summary Register Isum

Software Interrupt Request Register Fields Description

12Internal Processor Registers

Hardware Interrupt Clear Register Hwintclr

7describes the interrupt summary register fields

Interrupt Summary Register Fields Description

Mchkd W1C

Exception Summary Register Excsum

8describes the hardware interrupt clear register fields

Hardware Interrupt Clear Register Fields Description

Exception Summary Register Fields Description

9describes the exception summary register fields

14Internal Processor Registers

10 PAL Base Register Fields Description

PAL Base Register Palbase

Ibox Control Register Ictl

10describes the PAL base register fields

11 Ibox Control Register Fields Description

11describes the Ibox control register fields

16Internal Processor Registers

PCT0EN

Singleissueh

STWAIT64K

PCT1EN

Spce

Ibox Status Register Istat

18Internal Processor Registers

TRP

12describes the Ibox status register fields

12 Ibox Status Register Fields Description

MIS

20Internal Processor Registers

Clear Virtual-to-Physical Map Register Clrmap

Sleep Mode Register Sleep

Icache Flush Register Icflush

Icache Flush ASM Register Icflushasm

14 Process Context Register Fields Description

14describes the process context register fields

22Internal Processor Registers

15describes the performance counter control register fields

Performance Counter Control Register Pctrctl

15 Performance Counter Control Register Fields Description

SL0

Pctxppce

Pmstalled

Pmkilledbm

16 Performance Counter Control Register Input Select Fields

Mbox IPRs

Mbox IPRs

DTB Tag Array Write Registers 0 and 1 DTBTAG0, DTBTAG1

17describes the Dtbaltmode register fields

DTB Alternate Processor Mode Register Dtbaltmode

17 DTB Alternate Processor Mode Register Fields Description

DTB PTE Array Write Registers 0 and 1 DTBPTE0, DTBPTE1

ALTMODE10

Dstream TB Invalidate All Process ASM=0 Register Dtbiap

Dstream TB Invalidate All Register Dtbia

Dstream TB Invalidate Single Registers 0 and 1 DTBIS0,1

18 Memory Management Status Register Fields Description

Dstream TB Address Space Number Registers 0 and 1 DTBASN0,1

Memory Management Status Register Mmstat

18describes the memory management status register fields

For

Mbox Control Register Mctl

ACV

19 Mbox Control Register Fields Description

Erences to superpages result in access violations

Dcache Control Register Dcctl

19describes the Mbox control register fields

20describes the Dcache control register fields

Dcache Status Register Dcstat

20 Dcache Control Register Fields Description

21 Dcache Status Register Fields Description

Cbox CSRs and IPRs

Cbox CSRs and IPRs

21describes the Dcache status register fields

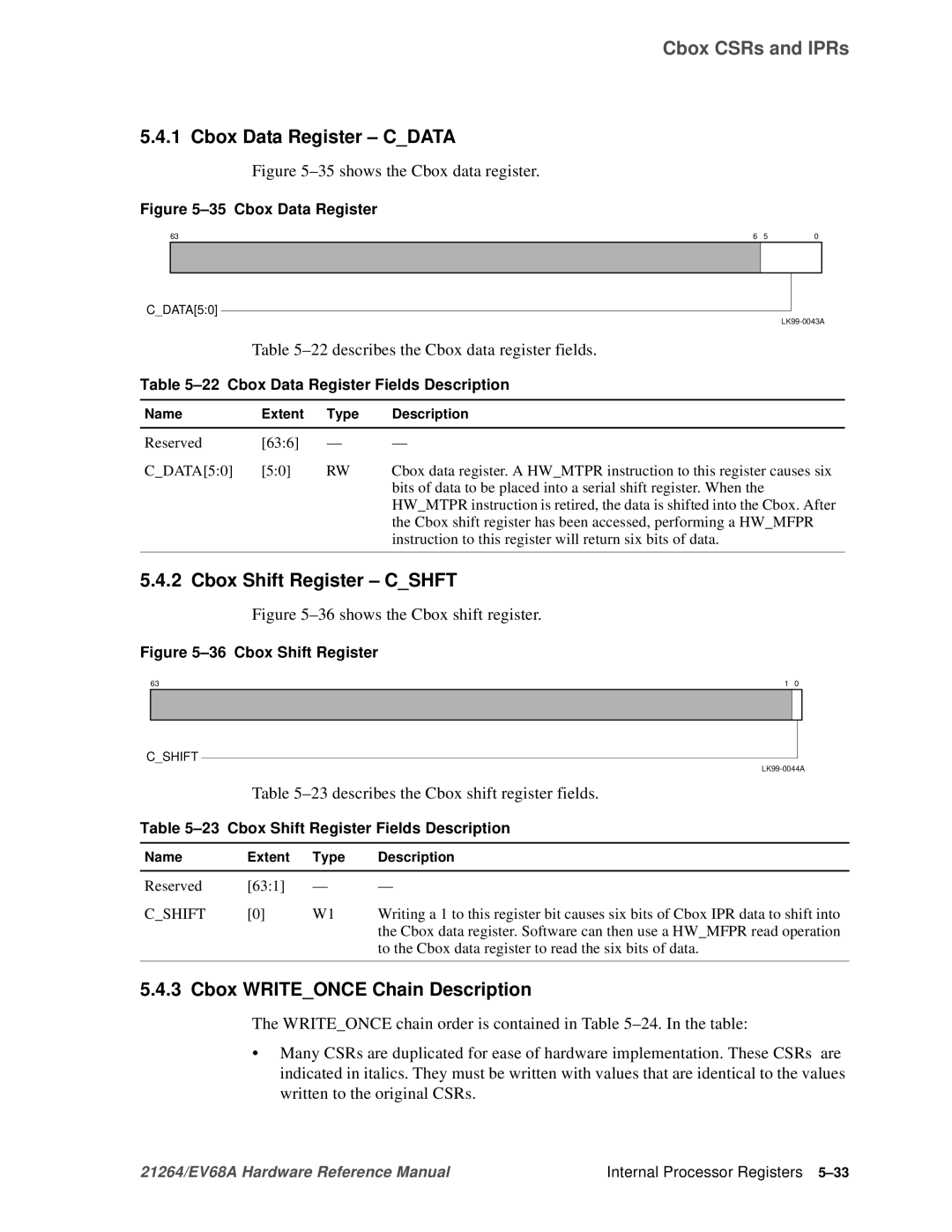

22 describes the Cbox data register fields

Cbox Data Register Cdata

Cbox Shift Register Cshft

Cbox Writeonce Chain Description

34Internal Processor Registers

24 Cbox Writeonce Chain Order

Mboxbcprbstall BCLATDATAPATTERN031 BCLATTAGPATTERN023

BCWRRDBUBBLES03

36Internal Processor Registers

SYSCLKDELAY10

38Internal Processor Registers

Cbox Writemany Chain Description

25 Cbox Writemany Chain Order

40Internal Processor Registers

26 Cbox Read IPR Fields Description

Cbox Read Register IPR Description

0 1 1 Istreammemerr

0 1 1 Dstreammemerr

PALcode Description

Privileged Architecture Library Code

Privileged Architecture Library Code

PALmode Environment

PALmode Environment

Hwld Instruction

Required PALcode Function Codes

Opcodes Reserved for PALcode

Required PALcode Function Codes

Hwld Instruction Fields Descriptions

Opcodes Reserved for PALcode

Hwst Instruction

3describes the Hwld instruction fields

4describes the Hwst instruction fields

Hwret Instruction

Hwst Instruction Fields Descriptions

Hint

Hwmfpr and Hwmtpr Instructions

5describes the Hwret instruction fields

Hwret Instruction Fields Descriptions

Hwmfpr and Hwmtpr Instructions Fields Descriptions

Internal Processor Register Access Mechanisms

Internal Processor Register Access Mechanisms

6describes the Hwmfpr and Hwmtpr instructions fields

Hardware Structure of Explicitly Written IPRs

IPR Scoreboard Bits

Hardware Structure of Implicitly Written IPRs

IPR Access Ordering

Paired Instruction Fetch Order

10Privileged Architecture Library Code

PALcode Emulation of the Fpcr

PALshadow Registers

PALshadow Registers

PALcode Entry Points

PALcode Entry Points

PALcode Exception Entry Locations

PALcode Exception Entry Points

14Privileged Architecture Library Code

Translation Buffer TB Fill Flows

Translation Buffer TB Fill Flows

DTB Fill

Tb miss

Wr Data

Wr PTE LD-PTE, write TB

16Privileged Architecture Library Code

ITB Fill

Performance Counter Support

Performance Counter Support

IPRs Used for Performance Counter Support

General Precautions

Aggregate Mode Programming Guidelines

Aggregate Mode Precautions

SL1

10 Aggregate Mode Returned IPR Contents

Operation

Pctrctl SL0

11shows the counter modes that are used with Aggregate mode

ProfileMe Mode Programming Guidelines

This input counts Mbox replay traps

12 Cmov Decomposed

22Privileged Architecture Library Code

13 ProfileMe Mode Returned IPR Contents

Inum retire delay cycles

ProfileMe Counting Mode Description Cycle counting

24Privileged Architecture Library Code

14shows the counter modes that are used with ProfileMe mode

Counter Modes for ProfileMe Mode

14 ProfileMe Mode Pctrctl Input Select Fields

Initialization and Configuration

Initialization and Configuration

Power-Up Reset Flow and the ResetL and Dcokh Pins

21264/EV68A Reset State Machine Major Operations

Constraints

Power-Up Reset Flow and the ResetL and Dcokh Pins

Signal Pin Reset State

Power Sequencing and Reset State for Signal Pins

Pllvdd

Clock Forwarding and System Clock Ratio Configuration

PLL

Pin Signal Names and Initialization State

BiST and Srom Load and the TestStatH Pin

PLL Ramp Up

Power-Up Flow Signals and Their Constraints

Clock Forward Reset and System Interface Initialization

EV68A

Fault Reset Flow

Fault Reset Flow

Effect on IPRs After Fault Reset

Energy Star Certification and Sleep Mode Flow

Energy Star Certification and Sleep Mode Flow

10Initialization and Configuration

Effect on IPRs After Transition Through Sleep Mode

Effect on IPRs After Warm Reset

Warm Reset Flow

Warm Reset Flow

Signals and Constraints for the Sleep Mode Sequence

Array Initialization

Initialization Mode Processing

12Initialization and Configuration

Array Initialization

Evictenable BCWRTSTS30 Bcbankenable

Initialization Mode Processing

External Interface Initialization

Internal Processor Register Power-Up Reset State

10 Internal Processor Registers at Power-Up Reset State

14Initialization and Configuration

Internal Processor Register Power-Up Reset State

16Initialization and Configuration

Ieee 1149.1 Test Port Reset

Reset State Machine

Ieee 1149.1 Test Port Reset

11 21264/EV68A Reset State Machine State Descriptions

Reset State Machine

18Initialization and Configuration

PLL Output Clocks

Phase-Lock Loop PLL Functional Description

Phase-Lock Loop PLL Functional Description

Differential Reference Clocks

20Initialization and Configuration

Power-Up/Reset Clocking

21264/EV68A Error Detection Mechanisms

Error Detection and Error Handling

Error Detection and Error Handling

Data Error Correction Code

Data Error Correction Code

Icache Data or Tag Parity Error

Dcache Tag Parity Error

Dcache Data Single-Bit Correctable ECC Error

Dcache Data Single-Bit Correctable ECC Error

Load Instruction

Store Instruction Quadword or Smaller

Dcache Store Second Error

Dcache Duplicate Tag Parity Error

Dcache Store Second Error

Controlling Bcache Block Parity Calculation

Bcache Tag Parity Error

Bcache Data Single-Bit Correctable ECC Error

Bcache Tag Parity Error

Dcache Fill from Bcache

Bcache Data Single-Bit Correctable ECC Error

Icache Fill from Memory

Memory/System Port Single-Bit Data Correctable ECC Error

Memory/System Port Single-Bit Data Correctable ECC Error

Bcache Victim Read

Dcache Fill from Memory

Double-Bit Fill Errors

Bcache Data Single-Bit Correctable ECC Error on a Probe

Bcache Data Single-Bit Correctable ECC Error on a Probe

Section D.36

Error Case Summary

Error Case Summary

3summarizes the various error cases and their ramifications

Mchk Cstatistreambcdbl

Mchk Cstatistreammemerr

Cstatdstreammemerr

CRD Cstatprobebcerr

Page

Maximum Electrical Ratings

Electrical Characteristics

Electrical Data

1lists the maximum electrical ratings for the 21264/EV68A

Idcpower

DC Characteristics

DC Characteristics

Signal Types

Input Differential Amplifier Clock Receiver Idaclk

VDD Idcpower

Input DC Reference Pin Idcref

Input Differential Amplifier Receiver IDA

Codtp

Pin Type Open-Drain Driver for Test Pins Oodtp

Pin Type Open-Drain Output Driver OOD

IOZ

12 Push-Pull Output Clock Driver Oppclk

11 Push-Pull Output Driver OPP

AC Characteristics

AC Characteristics

AC Test Conditions

TSU1 TDH2

13 AC Specifications

Dcokh

AC Characteristics

Page

That causes thermal failure

Operating Temperature

Operating Temperature at Heat Sink Center Tc

Thermal Management

Θca at Various Airflows for 21264/EV68A

Operating Temperature

10-2Thermal Management

Heat Sink Specifications

Heat Sink Specifications

10-4Thermal Management

Type 2 Heat Sink

Type 3 Heat Sink

Thermal Design Considerations

Thermal Design Considerations

10-6Thermal Management

Testability and Diagnostics

Testability and Diagnostics

Test Pins

Dedicated Test Port Pins

Srom Load Operation

SROM/Serial Diagnostic Terminal Port

SROM/Serial Diagnostic Terminal Port

11-2Testability and Diagnostics

Ieee 1149.1 Port

Ieee 1149.1 Port

Ieee 1149.1 Instructions and Opcodes

TAP Controller State Machine

11-4Testability and Diagnostics

TestStatH Pin

TestStatH Pin

Srom Initialization

Power-Up Self-Test and Initialization

Power-Up Self-Test and Initialization

Built-in Self-Test

Serial Instruction Cache Load Operation

11-6Testability and Diagnostics

Icache Bit Fields in an Srom Line

See Appendix B for a listing of the Boundary-Scan Register

References

Page

Alpha Instruction Set A-1

Alpha Instruction Set

Alpha Instruction Summary

Table A-1 Instruction Format and Opcode Notation

Alpha Instruction Summary

Opr 11.46 Cmove if ≥ zero

Mbr Branch to subroutine

Pcd Trap to PALcode

Opr 11.24 Cmove if = zero

15.0BE Convert quadword to Gfloating

15.0AF Convert Gfloating to quadword

17.010 Convert longword to quadword

15.0BC Convert quadword to Ffloating

17.02B Fcmove if ≠ zero

17.02F Fcmove if zero

17.02E Fcmove if ≤ zero

17.02C Fcmove if zero

Mem Load Sfloating

Opr 13.40 Multiply longword with integer overflow enable

Opr 13.60 Multiply quadword with integer overflow enable

Opr 1C.31 Pixel error

Opr 10.02 Scaled add longword by

Opr 1C.36 Pack words to bytes Mfc 18.E000 Read and clear

Mbr 1A.2 Return from subroutine

Mfc 18.C000 Read process cycle counter 18.F000 Read and set

Reserved Opcodes

Reserved Opcodes

Opcodes Reserved for Compaq

Ieee Floating-Point Instructions

Ieee Floating-Point Instructions

Opcodes Reserved for PALcode

12B 16B

08B 00B 04B

18B 10B 14B

02B 06B

Independent Floating-Point Instructions

VAX Floating-Point Instructions

VAX Floating-Point Instructions

Opcode Summary

Opcode Summary

Floating-point operate instruction opcodes

Mem Table A-9explains the symbols used in Table A-8

Mem Res

Ieee floating-point instruction opcodes

Ieee Floating-Point Conformance

Ieee Floating-Point Conformance

14Alpha Instruction Set

Alpha Instruction Set A-15

Table A-11 Exceptional Input and Output Conditions

16Alpha Instruction Set

Cmptlt Cmptle Input

Cmpteq Cmptun Input

Alpha Instruction Set A-17

Fbeq Fbne Fblt Fble Fbgt Fbge LDS LDT STS STT Cpys Cpysn

Boundary-Scan Register

21264/EV68A Boundary-Scan Register

Pllvdd

Boundary-Scan Register

21264/EV68A Boundary-Scan Register B-3

421264/EV68A Boundary-Scan Register

21264/EV68A Boundary-Scan Register B-5

621264/EV68A Boundary-Scan Register

21264/EV68A Boundary-Scan Register B-7

821264/EV68A Boundary-Scan Register

21264/EV68A Boundary-Scan Register B-9

1021264/EV68A Boundary-Scan Register

21264/EV68A Boundary-Scan Register B-11

1221264/EV68A Boundary-Scan Register

Serial Icache Load Predecode Values C-1

Serial Icache Load Predecode Values

Page

PALcode Restrictions and Guidelines D-1

PALcode Restrictions and Guidelines

2PALcode Restrictions and Guidelines

PALcode Restrictions and Guidelines D-3

4PALcode Restrictions and Guidelines

Initwritemany

PALcode Restrictions and Guidelines D-5

6PALcode Restrictions and Guidelines

PALcode Restrictions and Guidelines D-7

8PALcode Restrictions and Guidelines

PALcode Restrictions and Guidelines D-9

Restriction 7 Replay Trap, Interrupt Code Sequence, and STF

10PALcode Restrictions and Guidelines

Restriction 10 Duplicate IPR Mode Bits

Restriction 9 PALmode Istream Address Ranges

Restriction 9 PALmode Istream Address Ranges

Restriction 14 Hwret

Restriction 11 Ibox IPR Update Synchronization

Restriction 11 Ibox IPR Update Synchronization

Restriction 13 DTB Fill Flow Collision

Guideline 16 JSR-BAD VA

Guideline 20 Ictlsbe Stream Buffer Enable

Guideline 16 JSR-BAD VA

Restriction 21 HWRET/STALL After Hwmtpr ASN0/ASN1

Restriction 22 HWRET/STALL After Hwmtpr IS0/IS1

Restriction 22 HWRET/STALL After Hwmtpr IS0/IS1

PALcode Restrictions and Guidelines D-13

14PALcode Restrictions and Guidelines

Restriction 25 Hwmtpr Itbia After Reset

Guideline 26 Conditional Branches in PALcode

Restriction 24 HWRET/STALL After Hwmtpr ICFLUSH, Icflushasm

Restriction 30 Hwmtpr and Hwmfpr to the Cbox CSR

Guideline 29 JSR, JMP, RET, and Jsrcor in PALcode

PALcode Restrictions and Guidelines D-15

16PALcode Restrictions and Guidelines

Restriction 30 Hwmtpr and Hwmfpr to the Cbox CSR

PALcode Restrictions and Guidelines D-17

Restriction 31 ICTLVA48 Update

Restriction 32 Pctrctl Update

Restriction 31 ICTLVA48 Update

Restriction 37 Updating VACTLVA48

Guideline 35 Hwintclr Update

Restriction 33 Hwld Physical/Lock Use

Restriction 36 Updating Ictlsde

PALcode Restrictions and Guidelines D-19

Restriction 40 Scrubbing a Single-Bit Error

20PALcode Restrictions and Guidelines

Restriction 40 Scrubbing a Single-Bit Error

Restriction 43 No Trappable Instructions Along with

Restriction 42 Updating VACTL, CCCTL, or CC IPRs

PALcode Restrictions and Guidelines D-21

22PALcode Restrictions and Guidelines

Restriction 47 Cache Eviction for Single-Bit Cache Errors

PALcode Restrictions and Guidelines D-23

Restriction 47 Cache Eviction for Single-Bit Cache Errors

24PALcode Restrictions and Guidelines

Forwarding Clock Pin Groupings

21264/EV68A-to-Bcache Pin Interface

Table E-1 Bcache Forwarding Clock Pin Groupings

Tag Pin Usage

Late-Write Non-Bursting SSRAMs

Late-Write Non-Bursting SSRAMs

Data Pin Usage

Dual-Data Rate SSRAMs

Dual-Data Rate SSRAMs

Table E-4 Dual-Data Rate Ssram Data Pin Usage

Table E-5 Dual-Data Rate Ssram Tag Pin Usage

Trstl

421264/EV68A-to-Bcache Pin Interface

21264/EV68A-to-Bcache Pin Interface E-5

Page

Glossary

BIU

BSR

Cisc

CSR

Cmos

CPI

CPU

DTL

DMA

Dram

DTB

Fpga

Feprom

FET

FEU

IDU

Gclk

Jfet

Iowb

Ipga

ITB

Mips

MAF

MBO

MBZ

Nvram

MSI

Naturally Aligned

Nmos

Plcc

PAL

PGA

PLA

RAS

Pqfp

Prom

RAM

SAM

Risc

ROM

RTL

Sipp

Sdram

Simm

SIP

Unaligned

Stram

TTL

Uart

VDF

Unpredictable

Uvprom

VAF

Writeblock

WAR

Numerics

Index

Index-2

Index-3

Index-4

ECC

Index-6

Index-7

Index-8

Index-9

Index-10

Index-11

Index-12