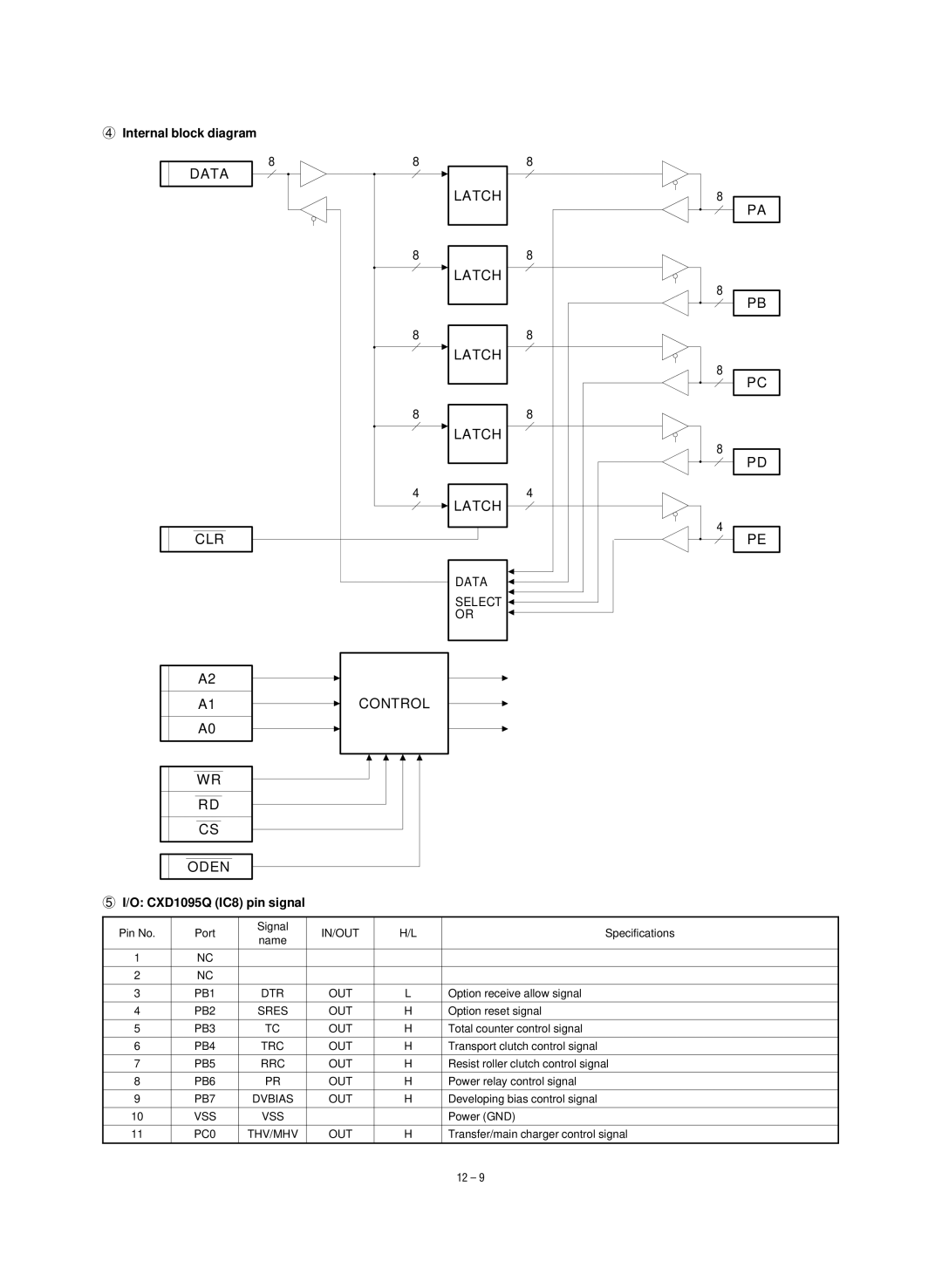

4Internal block diagram

8

DATA

CLR

88

LATCH |

8 | 8 |

| LATCH |

8 | 8 |

| LATCH |

8 | 8 |

| LATCH |

4 | 4 |

| LATCH |

DATA

SELECT ![]()

OR

8 |

PA |

8 |

PB |

8 |

PC |

8 |

PD |

4 |

PE |

A2

A1

A0

WR

RD

CS

ODEN

CONTROL

5I/O: CXD1095Q (IC8) pin signal

Pin No. | Port | Signal | IN/OUT | H/L | Specifications | |

name | ||||||

|

|

|

|

| ||

|

|

|

|

|

| |

1 | NC |

|

|

|

| |

|

|

|

|

|

| |

2 | NC |

|

|

|

| |

|

|

|

|

|

| |

3 | PB1 | DTR | OUT | L | Option receive allow signal | |

|

|

|

|

|

| |

4 | PB2 | SRES | OUT | H | Option reset signal | |

|

|

|

|

|

| |

5 | PB3 | TC | OUT | H | Total counter control signal | |

|

|

|

|

|

| |

6 | PB4 | TRC | OUT | H | Transport clutch control signal | |

|

|

|

|

|

| |

7 | PB5 | RRC | OUT | H | Resist roller clutch control signal | |

|

|

|

|

|

| |

8 | PB6 | PR | OUT | H | Power relay control signal | |

|

|

|

|

|

| |

9 | PB7 | DVBIAS | OUT | H | Developing bias control signal | |

|

|

|

|

|

| |

10 | VSS | VSS |

|

| Power (GND) | |

|

|

|

|

|

| |

11 | PC0 | THV/MHV | OUT | H | Transfer/main charger control signal | |

|

|

|

|

|

|

12 – 9