SUB DC | VH |

| 1 |

|

| ||

|

|

| |

PWB | VB |

| 2 |

|

| ||

|

|

| |

| IC4 | VD | 3 |

|

|

2

CLUTCH

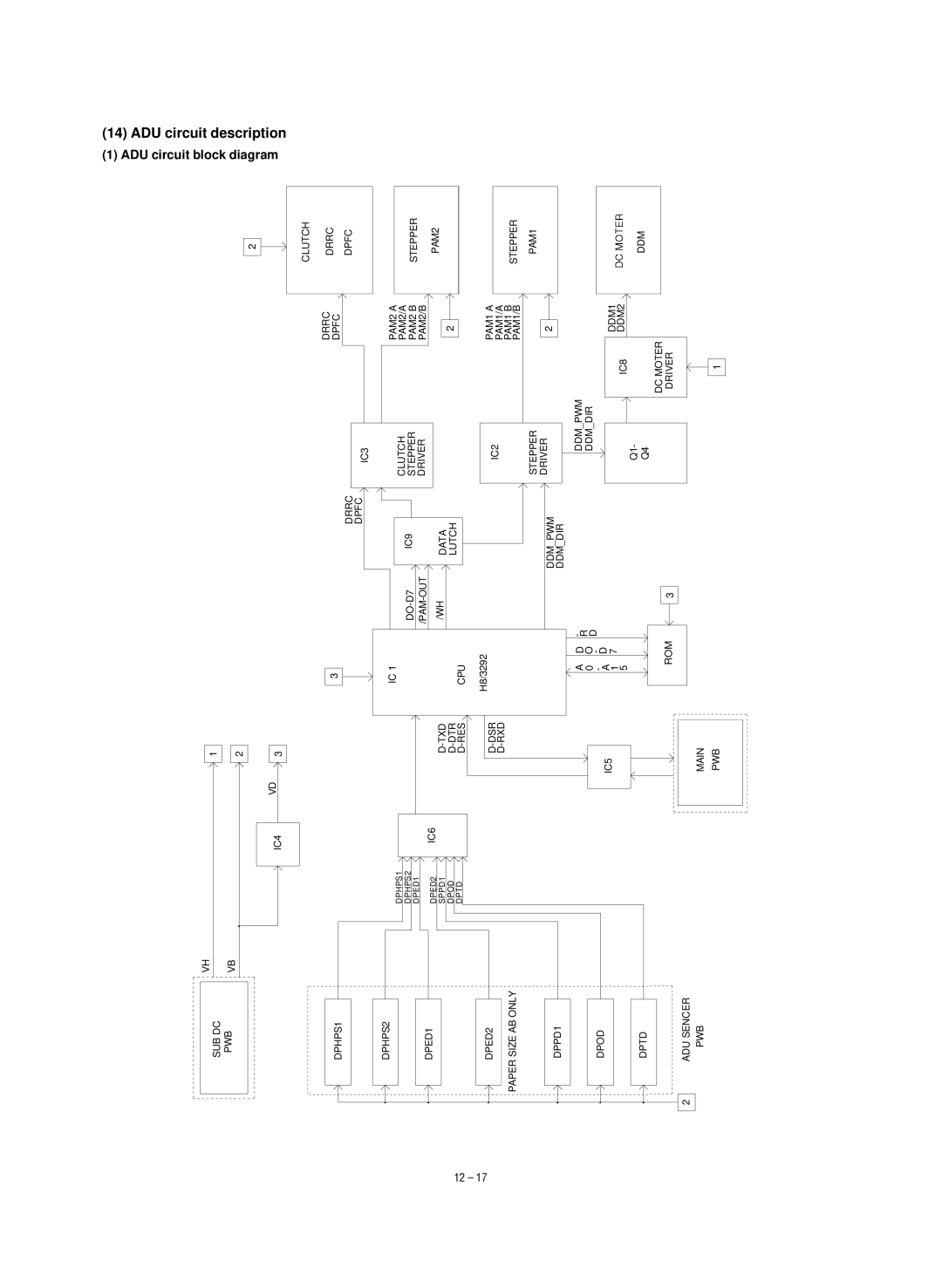

(1) ADU circuit block diagram | (14) ADU circuit description |

12 – 17

DPHPS1

DPHPS2

DPED1

DPED2

![]() PAPER SIZE AB ONLY

PAPER SIZE AB ONLY ![]()

DPPD1

DPOD

DPTD

2ADU SENCER PWB

DPHPS1 |

|

DPHPS2 |

|

DPED1 |

|

DPED2 | IC6 |

SPPD1 |

|

DPOD |

|

DPTD |

|

IC5 |

MAIN

PWB

3 |

|

|

|

| DRRC |

|

|

|

| DPFC | |

|

|

| DRRC |

|

|

|

|

| DPFC | IC3 |

|

|

|

|

|

| |

IC 1 |

|

|

| CLUTCH | PAM2 A |

|

| IC9 | PAM2/A | ||

|

| STEPPER | PAM2 B | ||

|

|

| DRIVER | PAM2/B | |

|

| /WH | DATA |

| 2 |

CPU |

|

| LUTCH |

| |

|

|

|

|

| |

H8/3292 |

|

|

|

| PAM1 A |

|

|

|

| IC2 | |

|

|

|

| PAM1/A | |

|

|

|

|

| |

|

|

|

|

| PAM1 B |

|

|

|

|

| PAM1/B |

|

|

|

| STEPPER |

|

|

|

| DDM_PWM | DRIVER | 2 |

|

|

|

| ||

|

|

| DDM_DIR |

|

|

A | D | - |

| DDM_PWM |

|

0 | O | R |

| DDM_DIR |

|

D |

|

| |||

- | - |

|

|

| |

A | D |

|

|

| DDM1 |

1 | 7 |

|

| IC8 | |

5 |

|

|

| DDM2 | |

|

|

|

| Q1- |

|

|

|

|

| Q4 |

|

ROM |

|

| DC MOTER |

| |

3 |

| DRIVER |

| ||

|

|

|

| 1 |

|

DRRC

DPFC

STEPPER

PAM2

STEPPER

PAM1

DDM